DDR3带宽的计算

judy 在 周五, 08/18/2023 - 14:39 提交

本文总结了DDR3带宽的计算方法

本文总结了DDR3带宽的计算方法

带宽是影响FPGA加速器的重要因素,因为大量的并行计算对数据量要求很大。如果加速器对数据的访问是不规则的,那么cache miss就会大大影响加速器性能。这篇来自FPGA2019会议的报告,向我们展示了如何来更好的处理cache miss问题,提高对缓存的利用率以及提高加速器效率

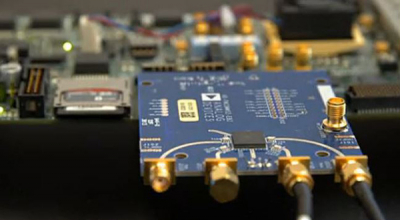

本入门文章由两部分组成,旨在介绍JESD204C标准,着重说明其与JESD204B的不同之处,并详细阐明为达成上述目标、提供对用户更友好的接口、实现各行各业的带宽能力需求而引入的关键新特性。本系列的第一部分概述版本差异和新特性,第二部分将深入探讨最重要的新特性

112G PAM4 是业界通向更高带宽的下一步。该演示主要介绍 Xilinx 针对新一代系统提供 112G 的远景。