开发者分享 | 巧用方法论

judy 在 周四, 10/14/2021 - 15:36 提交

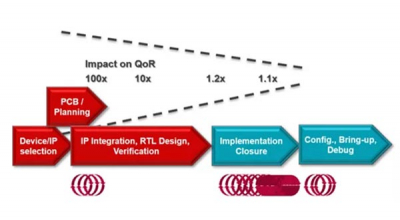

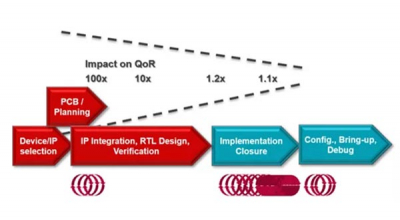

“方法论 (Methodology)” 报告是 Vivado 工具中的一项功能,它使用 UltraFast 设计方法论 (UFDM) 以及 Versal ACAP 设计方法论来帮助精简设计进程和提升 QoR。方法论分析是一种特殊形式的设计规则检查,专用于检查是否符合设计方法论,并识别进程中出现的常见错误。

“方法论 (Methodology)” 报告是 Vivado 工具中的一项功能,它使用 UltraFast 设计方法论 (UFDM) 以及 Versal ACAP 设计方法论来帮助精简设计进程和提升 QoR。方法论分析是一种特殊形式的设计规则检查,专用于检查是否符合设计方法论,并识别进程中出现的常见错误。

本篇博文中的分析是根据真实客户问题撰写的,该客户发现在现场出现罕见的比特翻转, 本篇博文旨在演示用于缩小根本原因范围以及修复此问题的部分调试技巧。

本篇博文中的分析是根据真实客户问题撰写的,该客户发现硬件中存在 DDR4 校准错误,不同板以及不同构建 (build) 之间出现的故障并不一致。本篇博文旨在演示用于缩小根本原因范围以及修复此问题的部分调试技巧。

本篇博文中的分析是根据真实客户问题撰写的,该客户发现不同操作系统间 QoR 性能存在差异。虽然可以理解赛灵思无法保证不同操作系统间的可重复性,正如"赛灵思答复记录 61599"中所述,但此处案例中出现的差异量级值得进一步深入调查。

本篇博文中的分析是根据客户真实问题撰写的,该客户发现即使时序已得到满足的情况下,硬件功能仍出现错误。最后发现,问题与时钟域交汇 (Clock Domain Crossing) 有关,因此,本篇博文介绍了如何调试设计中的时钟域交汇问题。