如何减少时序报告中的逻辑延迟

judy 在 周二, 08/15/2023 - 09:57 提交

在FPGA逻辑电路设计中,FPGA设计能达到的最高性能往往由以下因素决定

在FPGA逻辑电路设计中,FPGA设计能达到的最高性能往往由以下因素决定

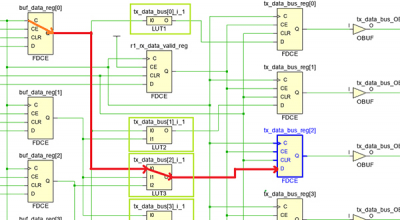

最近研究vivado里的时序分析路径时,发现了3个很有意思的问题

为了更精确地进行时序分析,设计者还必须设定一些与运行环境相关的可预测变量和随机变量

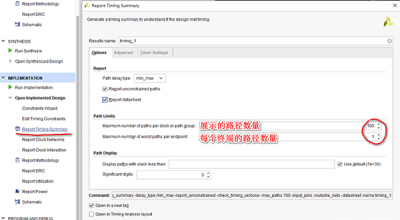

今天就通过一个简单的工程来看下如何在vivado软件中查看时序报告

衍生时钟约束必须指定时钟源,在对衍生时钟进行约束时,并不指直接对其周期

主时钟约束,就是我们对主时钟(Primary Clock)的时钟周期进行约束

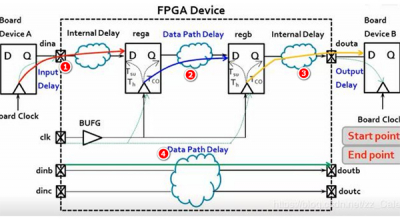

路径1、2、3实际上都是对寄存器到寄存器之间的数据路径之间的约束,而路径4则是约束纯组合逻辑

保持时间是对触发器而言,以能够稳定准确的锁存或者触发为目的

本篇文章我们将通过vivado工程实例来向大家介绍如何读懂时序分析报告。

以上升沿锁存为例,建立时间(Tsu)是指在时钟翻转之前输入的数据D必须保持稳定的时间。