Xilinx KU系列三速以太网IP核RGMII时序约束方法

judy 在 周二, 03/07/2023 - 14:45 提交

基于RGMII时序广泛应用于以太网通信中,基于Xilinx的三速以太网时序分析,不同的Xilinx系列方法不一样

基于RGMII时序广泛应用于以太网通信中,基于Xilinx的三速以太网时序分析,不同的Xilinx系列方法不一样

创建时钟是针对代码中主时钟而言,创建时钟之前需要知道代码中的主时钟都是什么

一个设计的时序报告中,design run 时序有红色,裕量(slack)为负数时

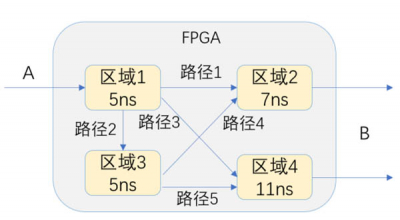

最近研究vivado里的时序分析路径时,发现了3个很有意思的问题

为了更精确地进行时序分析,设计者还必须设定一些与运行环境相关的可预测变量和随机变量

在调试时序约束的过程中,用户常常会对除了顶层约束外所涉及的繁杂的时序约束感到困惑而无从下手。

今天我们就来详细分析一下,这个约束应该如何使用。

这个专栏,我会从时序分析、时序约束和时序收敛3个方面来一起学习基于Xilinx FPGA和Vivado开发平台的FPGA时序相关内容。

在Vivado或其他综合工具(如Synplify)上,综合阶段需要添加什么约束呢?

本文章探讨一下FPGA的时序约束步骤