Vivado中怎么做set_input_delay约束

guanxiao_505740 在 周五, 12/24/2021 - 11:10 提交

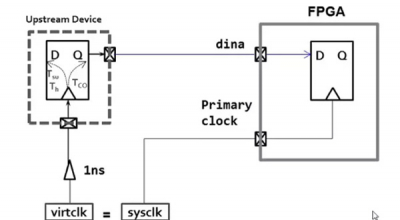

在STA中,要分析上游器件和FPGA之间的时序关系就得指定input delay。

在STA中,要分析上游器件和FPGA之间的时序关系就得指定input delay。

在我之前写的FPGA时序约束教程中,有一篇中讲到了虚拟时钟,但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。

在FPGA的开发中,对于两个异步时钟,如果我们可以在RTL的设计中保证这两个时钟域之间的处理都是正确的,那就可以让工具不分析这两个时钟域之间的交互。

Xilinx 建议将时序约束和物理约束分开保存为两个不同的文件。甚至可以将针对某一个模块的约束单独保存在一个文件中。可以使用 USED_IN_SYNTHESIS 和 USED_IN_IMPLEMENTATION 属性指定约束文件是在综合或实现过程中使用。

如果给 DCM/PLL/MMCM 的输入时钟施加 PERIOD 约束,约束会自动传递给输出时钟。这些时钟被视为相关时钟而跨时钟域路径由时序分析器进行分析,我该如何从时序分析中排除跨时钟域路径呢?

本篇博文中的分析是根据真实客户问题撰写的,该客户发现硬件中存在 DDR4 校准错误,不同板以及不同构建 (build) 之间出现的故障并不一致。本篇博文旨在演示用于缩小根本原因范围以及修复此问题的部分调试技巧。

随着设计复杂度和调用IP丰富度的增加,在调试时序约束的过程中,用户常常会对除了自己设定的约束外所涉及的繁杂的时序约束感到困惑而无从下手。举个例子,我的XDC里面并没有指定set_false_path,为什么有些路径在分析时忽略了?我怎么去定位这些约束是哪里设定的?本文结合一个具体案例,阐述了如何追溯同一时钟域内partial false path的来源,希望为开发者的设计调试提供一些技巧和窍门。

本文详细介绍Vivado工具对FPGA设计进行逻辑和时序分析的特点,以及工具生成的报告和信息。讨论实现时序收敛的方法,包括审查时钟树和时序约束,设计底层规划,以及平衡运行时间和结果。

4月23日,Xilinx Adapt China:Vivado专场的第二天,赛灵思 Vivado专家团将带来连续三场的“设计收敛”技巧分享。从如何提高QoR(结果质量)的方法技巧、解决接受的时序问题工具,到功耗约束的最佳实践,诚意满满,技术干货一应俱全。

时序约束中的 set_input_delay/set_output_delay 约束一直是一个难点,无论是概念、约束值的计算,还是最终的路径分析,每一次都要费一番脑子。Vivado为方便用户创建输入输出接口的约束,整理出了一套非常实用的InputDelay/Output Delay Constraints Language Templates。