影响FPGA时序的进位链(Carry Chain),你用对了么?

demi 在 周二, 01/14/2020 - 11:13 提交

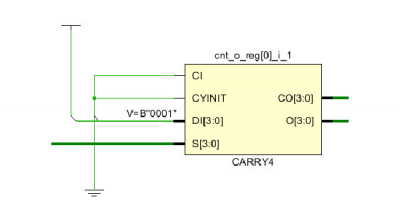

在FPGA中我们写的最大的逻辑是什么?相信对大部分朋友来说应该是计数器,从最初板卡的测试时我们会闪烁LED,到复杂的AXI总线中产生地址或者last等信号,都会用到计数器,使用计数器那必然会用到进位链。

在FPGA中我们写的最大的逻辑是什么?相信对大部分朋友来说应该是计数器,从最初板卡的测试时我们会闪烁LED,到复杂的AXI总线中产生地址或者last等信号,都会用到计数器,使用计数器那必然会用到进位链。

因为ZYNQ 的PS 和PL 部分的电源有上电顺序的要求,在电路设计中,按照ZYQN 的电源要求设计,上电依次为1.0V -> 1.8V -> 1.5 V -> 3.3V -> VCCIO

因为ZYNQ 的PS 和PL 部分的电源有上电顺序的要求,在电路设计中,按照ZYQN 的电源要求设计,上电依次为1.0V -> 1.8V -> 1.5 V -> 3.3V -> VCCIO

什么是时序约束?泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够满足我们的要求。因此如果我们不加时序约束,软件是无法得知我们的时钟周期是多少,PAR后的结果是不会提示时序警告的。

忠告一:如果时序差的不多,在1NS以内,可以通过修改综合,布局布线选项来搞定,如果差的多,就得动代码。

所谓普通时序系统(共同时钟系统)就是指驱动端和接收端的同步时钟信号都是由一个系统时钟发生器提供。

硬件描述语言(verilog,systemVerilog,VHDL等)不同于软件语言(C,C++等)的一点就是,代码对应于硬件实现,不同的代码风格影响硬件的实现效果。好的代码风格能让硬件“跑得更快”,而一个坏的代码风格则给后续时序收敛造成很大负担。

根据《UltraFAST 设计方法指南(适用于 Vivado Design Suite)》中的建议,本快捷参考指南提供了以下简化的分步骤快速收敛时序流程:初始设计检查;时序基线;时序违规解决。

在高速的同步电路设计中,时序决定了一切,要求所有时序路径都必须在约束限制的时钟周期内,这成为设计人员最大的难题,因此,首先确定和分析基本时序路径有助于设计者快速,准确地计算时序裕量,使系统稳定工作,XILINX公司提倡的几种常用基本路径。

FPGA中的时序问题是一个比较重要的问题,时序违例,尤其喜欢在资源利用率较高、时钟频率较高或者是位宽较宽的情况下出现。本文介绍时序分析的原理以及出现时序问题时一般的解决办法。