FPGA中降低时钟skew的几种方法

judy 在 周三, 03/13/2024 - 09:31 提交

首先哪些因此会导致时钟skew过大呢?

首先哪些因此会导致时钟skew过大呢?

ASIC 和FPGA芯片的内核之间最大的不同莫过于时钟结构。

xilinx提供了丰富的原语,可以将之看成FPGA开发可以使用的库函数,原语在FPGA中具有与之对应的硬件逻辑单元,但也注意,不同的FPGA的原语可能会有所不同

我们前面的两篇文章讲了7系列的时钟结构和clock region内部具体组成,这篇文章我们来讨论下MRCC和SRCC的区别。

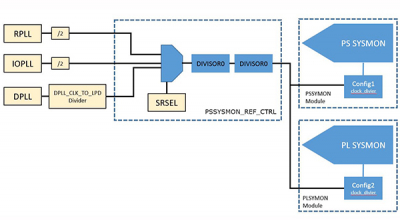

Zynq UltraScale+ MPSoC TRM 包含一个详细介绍 PS 及 PL SYSMON 时钟的部分。本答复记录详细描述了 PS 和 PL SYSMON 的时钟基础架构。

同相位时钟可以频率不同,但是时钟跳变沿是对齐的。如图所示,clk0为慢时钟,clk1为快时钟,clk0的时钟沿始终与clk1的时钟沿对齐,两个时钟相位相同。同源时钟,通常由一个PLL或者DLL产生,相位不需要相同,只要求相位固定。

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

在PS内的时钟模块可以为PL提供4个时钟FCLKCLK[3:0],这4个时钟的频率可以通过配置界面进行修改。由于这4个时钟的频率由PS引到PL中,所以可将FCLK连接到PL时钟缓冲区,作为PL内定制外设的时钟源。

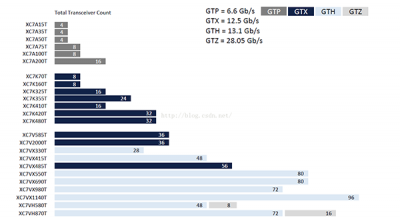

xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH以及GTZ四种串行高速收发器,四种收发器主要区别是支持的线速率不同。

时钟信号的处理是FPGA的特色之一,因此分频器也是FPGA设计中使用频率非常高的基本设计之一。一般在FPGA中都有集成的锁相环可以实现各种时钟的分频和倍频设计,但是通过语言设计进行时钟分频是最基本的训练,在对时钟要求不高的设计时也能节省锁相环资源。