实现高速收发器TX通道间相位对齐的方法

judy 在 周一, 01/30/2023 - 09:58 提交

本文将介绍两种实现相位对齐的方法,可适用于US系列和US Plus系列的GTH和GTY器件

本文将介绍两种实现相位对齐的方法,可适用于US系列和US Plus系列的GTH和GTY器件

随着数据带宽需求的持续增长,数据传输从并行变成串行,收发器的速率越来越高

不同芯片上使用的高速收发器也不同,而且同样是GTX,不同系列芯片上的速率也可能不同。比如7系列的FPGA,GTP最高可以达到6.6Gb/s,GTX最高12.5Gb/s,GTH最高13.1Gb/s,GTZ最高28.05Gb/s

本文描述了一种使用专用高速收发器的多速率串行接口。该设计基于非整数数据恢复单元,将数据速率下限扩展到0 Mb/s。

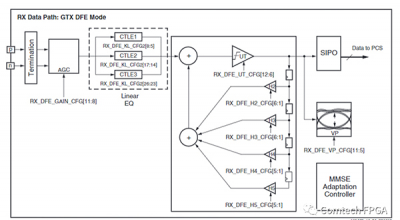

上一篇博文介绍了GTX的发送端,这一篇将介绍GTX的RX接收端,GTX RX接收端的结构和TX发送端类似,数据流方向相反,不过和发送端也有一些区别.....

每一个收发器拥有一个独立的发送端,发送端有PMA和PCS组成,其中PMA子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS子层包含8B/10B编解码、缓冲区、通道绑定和时钟修正等电路。

本来写了一篇关于高速收发器的初步调试方案的介绍,给出一些遇到问题时初步的调试建议。但是发现其中涉及到很多概念。逐一解释会导致文章过于冗长。所以单独写一篇基本概念的介绍,基于Xilinx 7系列的GTX

ADI Guneet Chadha演示如何使用电源系统管理使FPGA内核或I/O(例如:高速收发器)的电源输出电压(1V)保持在很小的容差范围内(0.25%)还显示了“如何确定电源裕量”