Zynq UltraScale+™ RFSoC DFE 数据表

judy 在 周四, 10/20/2022 - 17:23 提交

本文概述了Xilinx® Zynq® UltraScale+® RFSoC DFE的特点和产品选择。

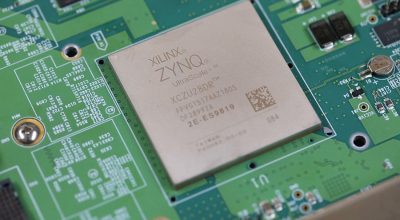

Zynq® UltraScale+™ RFSoC 在一款全可编程 SoC 架构中集成数千兆采样 RF 数据转换器和软判决前向纠错 (SD-FEC)。最新产品系列在一款 Zynq UltraScale+ 器件中提供 ARM® Cortex™-A53 处理子系统、UltraScale+ 可编程逻辑和最高信号处理带宽,能够提供综合 RF 信号链,满足无线、有线电视接入、测量测试、早期预警/雷达以及其它高性能 RF 应用需求

本文概述了Xilinx® Zynq® UltraScale+® RFSoC DFE的特点和产品选择。

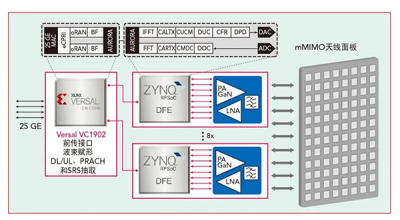

本文以面向mMIMO的有源天线单元架构和主要需求为重点,进一步对RU进行探讨。

ClockMatrix器件为AMD RFSoC DFE开发平台和O-RU参考设计提供同步及软件解决方案

5G新无线电(NR)网络的设计目的是与现有网络实现多年共存。在世界各地,营运商已投资数十亿美元建设2G/3G/4G网络,用于无线电设备和选址

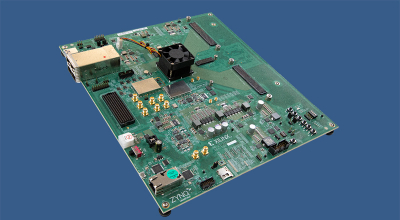

本视频介绍了套件中包含的主要板载组件和附件,并演示了如何对下一代 O-RAN 5G NR 架构进行原型设计。

该套件搭载 ZU67DR,是业界率先实现 8T8R、400MHz 瞬时带宽( IBW )的灵活应变单芯片 O-RU 解决方案。

该演示展示了 Xilinx DPD 性能,分别来自 Ampleon 和 Wolfspeed 的高功率驱动器和末级 PA。该演示展示了 Zynq RFSoC DFE 以及 Xilinx 最新 DPD IP 如何线性化用于 C 波段的高功率宏系列。

本文介绍针对超大规模系统的多通道应用,并将多输入多输出、波束成形和可控延迟与射频通道设计的其他经典要求相结合。

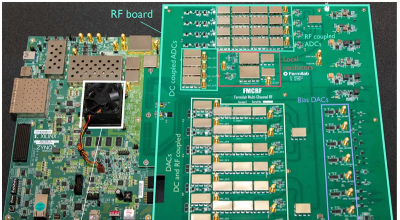

在某些应用中,必须在允许 GTIS 背景校准使用训练信号收敛后冻结 ADC 校准。

费米实验室,普林斯顿大学,芝加哥大学等科研机构联合发表了基于PYNQ RFSoC框架的开源量子位控制器-QICK (QuantumInstrumentation Control Kit),能够支持直接合成最高6GHz载波频率的控制脉冲。QICK包含Xilinx的ZCU111评估板,定制化的固件和软件和一个可选的定制化的模拟前端板。