探索在Zynq UltraScale上使用 Python的可能性

judy 在 周三, 09/07/2022 - 15:49 提交

本文将探讨如何以 Zynq UltraScale 器件上的 IP 核为目标,使用 Python 来创建一些强大的应用和实用工具。

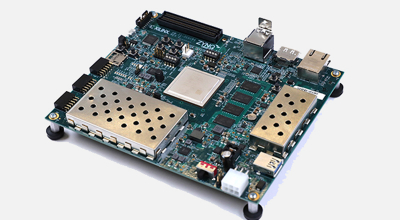

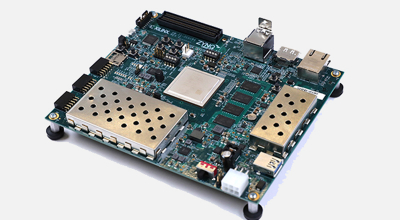

Zynq® UltraScale+™ MPSoC(多处理器系统芯片)是赛灵思(Xilinx)推出的一款集成了处理器系统和可编程逻辑的器件。这一系列芯片采用 UltraScale+ 架构,结合 ARM 处理器和可编程逻辑,为嵌入式系统提供了灵活性和高性能。

Zynq UltraScale+ MPSoC 适用于嵌入式系统设计,特别是对于需要高度定制和硬件加速的应用。它为设计人员提供了处理器和 FPGA 的集成解决方案,以满足各种复杂系统的需求。

本文将探讨如何以 Zynq UltraScale 器件上的 IP 核为目标,使用 Python 来创建一些强大的应用和实用工具。

Zynq UltraScale+ 的目标参考设计为经过全面验证的设计模块提供单独的知识产权和系统基础架构块

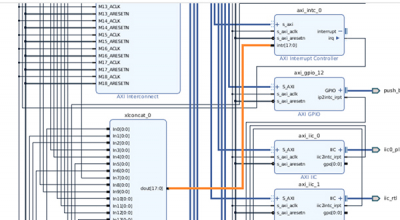

本篇博文主要讲解在 PL 中从 IP 核到 PS 之间需要完成含超 16 次中断的布线的情况下,该如何使用 AXI Interrupt Controller (INTC)

本文主要着重介绍了两个方面:如何从源码工程构建编译生成镜像文件和如何快速运行demo工程。

本文讨论的声纳发射器是一个相控阵发射器,能够发射10Khz至100Khz的频率。该系统采用了一个发射器模块阵列,每个模块能够驱动8个声纳传感器。

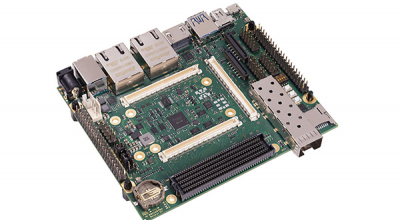

Canonical 工程师 Daniel van Vugt,最近对 AMD-Xilinx Kria KR260 和 GNOME Wayland 的协同工作产生了兴趣。

KV260 petalinux BSP在u-boot device tree中disable了GEM3,也就是说ethernet在u-boot中不建议使用ethernet。

一种高效的批量烧录AES keys和 RSA Keys 到EFUSE和BBRAM中的方法非常重要

本演示视频主要演示运行在 Zynq UltraScale+ MPSoC 上的可编程逻辑的视频处理加速。

本电子书将从当今机器人技术的常见挑战开始向您详细讲述何为机器人?以及目前所存在的设计挑战是什么?