AMD Xilinx AXI Interrupt Controller 中断优先级

judy 在 周二, 05/23/2023 - 17:02 提交

AXI Interrupt Controller支持中断优先级。 在Vivado Block Design中, bit-0连接的中断优先级最高

AXI Interrupt Controller支持中断优先级。 在Vivado Block Design中, bit-0连接的中断优先级最高

本节讨论 PS 和 PL 之间的连接,并探讨如何使用这些连接

Xilinx FPGA 内嵌的 CPU ,可以通过 AXI EPC 在 FPGA 芯片外接多个多种外设芯片

基于vivado2020.1和zcu102开发板(rev1.1)开发项目,工程涉及DDR4(MIG)和PL端多个读写接口交互的问题,通过AXI interconnect进行互联和仲裁(采用默认配置)。

在博客文章 使用 AXI performance monitors (APM)测试MPSoC DDR访问带宽 中介绍了DDR带宽测试工具"apm_main.elf"。使用过程中,发现还有些不足。它只能测试端口1/2/4/5,只能打印带宽。很多场合需要更多信息。于是更新了这个工具,可以测试所有端口

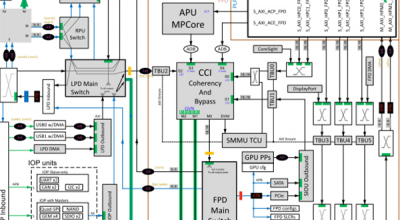

MPSoC的DDR控制器的数据通道上集成了 AXI performance monitors (APM)。具体情况,可以参考Xilinx UG1085 (v2.2)中Chapter 15的“Figure 15‐1: PS Interconnect”或者Figure 17-1。

在 AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,使用 C 语言在 HLS 中创建包含 AXI4-Lite 接口的 IP。在本篇博文中,我们将学习如何导出 IP 以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。

在 v2020.2 中,针对 AXI 主接口引入了 Vitis HLS 自动接口扩展选项,了解如何与使用端口上的矢量数据类型来显式描述端口宽度进行比较。

在 AMBA 系列之 AXI 总线协议初探 中,了解到 AXI 总线交互分为 Master / Slave 两端,而且标准的 AXI 总线支持不同的位宽,既然是总线,那么必须要支持总线互联,多 Master,多 Slave的场景

在上一篇中着重讲解了DMA的含义和AXI_DMA_IP,本次的重点就是搭建一个AXI_DMA环路工程,并从C语言角度分析其SDK代码