AXI总线简介(二)

demi 在 周三, 12/25/2019 - 15:46 提交

AXI协议是基于burst的,主机只给出突发传输的第一个字节的地址,从机必须计算突发传输后续的地址。突发传输不能跨4KB边界(防止突发跨越两个从机的边界,也限制了从机所需支持的地址自增数)。

AXI协议是基于burst的,主机只给出突发传输的第一个字节的地址,从机必须计算突发传输后续的地址。突发传输不能跨4KB边界(防止突发跨越两个从机的边界,也限制了从机所需支持的地址自增数)。

AXI4.0-lite是AXI的简化版本,ACE4.0 是AXI缓存一致性扩展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA进行以数据为主导的大量数据的传输应用。

由于ZYNQ架构和常用接口IP核经常出现 AXI协议,赛灵思的协议手册讲解时序比较分散。所以笔者收藏AXI协议的几种时序,方便编程。

在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议。其中三种AXI总线分别为

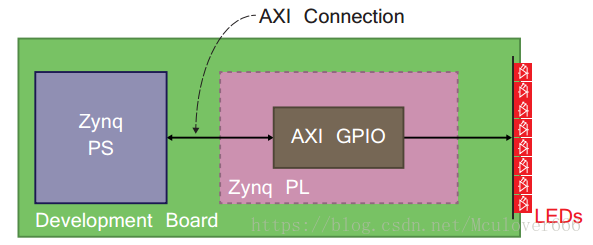

上一节中分别独立实验了Zynq的PS端和PL端,并初步实验了PS端先硬件再软件的开发流程和IP核设计的设计方法。第一节中提及到:Zynq是以PS端的ARM处理器系统为核心的,PS端和PL端是通过AXI总线,并且Xilinx已经提供了各种AXI通信的IP核,接下来的实验中将会更加明确的体验到利用IP核设计的设计方法。

1.实验目标

板载的LED和RGBLED都是接在PL端的,这个实验将利用PS端程序通过AXI总线控制连接在PL端的LED。

2.实验步骤

整个实验流程参考《The Zynq Book Tutorials》的chpt1:First Designs on Zynq(这本实验指导手册是英文的,但我个人认为英文原版要比中文看着清楚很多)。

上一节我们观察了AXI总线的信号,了解了基于AXI总线读写的时序,这一节我们继续探索基于AXI总线的设计,来看一看ZYNQ系列开发板的独特优势,PS可以控制PL产生定制化的行为,而不需要去动硬件代码。

zynq AXI是很重要的内容,本篇仅是简单的介绍。大量参考了其他书籍。

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一种总线协议, Xilinx从 6 系列的 FPGA 开始对 AXI 总线提供支持,目前使用 AXI4 版本。

1.AXI总线

ZYNQ有三种AXI总线: