带你快速入门AXI4总线--AXI4-Full篇(3):AXI4-Full接口IP源码仿真分析(Master接口)

judy 在 周二, 02/28/2023 - 09:35 提交

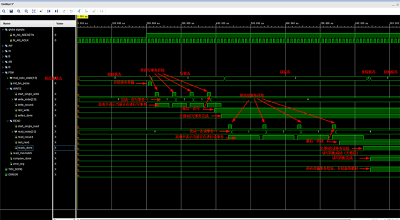

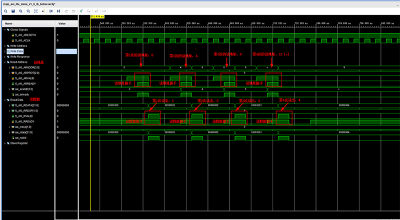

接slave接口篇,本文继续打包一个AXI4-Full-Master接口的IP,学习下源码,再仿真看看波形

接slave接口篇,本文继续打包一个AXI4-Full-Master接口的IP,学习下源码,再仿真看看波形

本文写AXI4-Full接口。AXI4-Full接口的源码基本与AXI4-Lite接口的源码一致

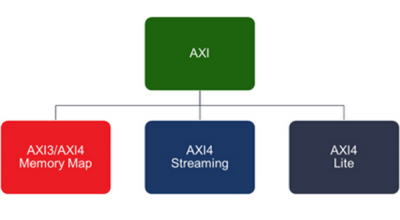

AXI 表示 Advanced eXtensible Interface(高级可扩展接口),它是由 Arm 定义的接口协议

在本文我们将生成AXI4-Lite_Master接口的IP来对其解析

AXI4 STREAM DATA FIFO也是一种先入先出形式的数据缓存队列

Vivado在打包IP核的时候提供了AXI4-Stream的接口,接下来分别例化两个IP

在这篇文章中,我们照葫芦画瓢,也打包2个AXI4-Lite接口的IP,来对其的仿真和原始代码学习一番

该系列先对AXI4-Stream协议及其使用做一个简单的介绍

在 Vivado 中自定义 AXI4-Lite 接口的 IP,实现一个简单的 LED 控制功能,并将其挂载到 AXI Interconnect 总线互联结构上,通过 ZYNQ 主机控制,后面对 Xilinx 提供的整个 AXI4-Lite 源码进行分析。

AXI4、AXI4-Lite和AXI4-Stream均使用Ready、Valid握手机制进行通信。信息传输的发起者使用Valid 信号指示数据何时有效,接收端产生 Ready 信号来表明已经准备好接收数据,当两者均为高时,启动传输。