使用 DMA 在 FPGA 中的 HDL 和嵌入式 C 之间传输数据

judy 在 周一, 11/27/2023 - 11:40 提交

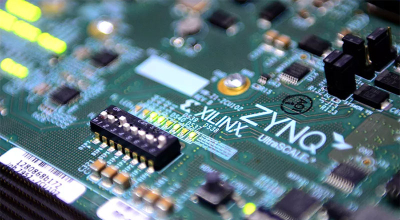

该项目介绍了如何在 PL 中的 HDL 与 FPGA 中的处理器上运行的嵌入式 C 之间传输数据的基本结构

该项目介绍了如何在 PL 中的 HDL 与 FPGA 中的处理器上运行的嵌入式 C 之间传输数据的基本结构

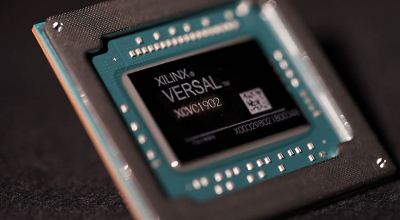

AMD FPGA自带PCIE硬核,实现了PCIE协议,把串行数据转换为并行的用户数据

前两周有人询问DMA下的cache操作和dma-coherent。以前零碎看过代码。

本文先介绍集中PL与PS的通信方法,然后重点介绍通过DMA实现PS与PL通信。

之前使用过xdma和qdma,但是未对其流程梳理,今天对其DMA操作流程梳理下,以备记录。

RIFFA 是一种开源通信架构,它允许通过 PCIe 在用户的 FPGA IP 内核和 CPU 的主存储器之间实时交换数据。为了建立其逻辑通道,RIFFA 在 CPU 端拥有一系列软件库,在 FPGA 端拥有 IP 核。本文主要针对其中的DMA性能(Scatter-Gather DMA)进行测试。

DMA是直接内存访问(Direct Memory Access),DMA引擎可以将数据从一个地方传输到另一个地方,在传输过程中不经过CPU的控制。最简单的DMA用法是将数据从内存的一个区域搬运到另一个区域。

DMA中断实例化函数,将要配置的DMA信息先lookupConfig再进行CfgInitialize,DMA采用块模式(Block mode),如果是Sg模式,则配置失败。定时器初始化函数,传入参数有定时器结构、加载值,设备ID。

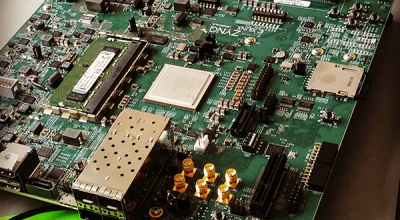

基于AXI的DMA对内部寄存器的读写有着相同的方式。在普通传输模式下,DMA内部的寄存器都是由处理器通过AXI-Lite总线进行读写的;但基于AXI总线的三种DMA,都增加了S/G传输模式,它卸载了处理器对寄存器的读写,通过独立的S/G读写通道对存储着命令描述符的内存进行访问读取、处理描述符,然后更新描述符写入内存。

几个常用的 AXI 接口 IP 的功能(上面已经提到):

AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HP<---->AXI-Stream 的转换

AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GP<----->AXI-Stream 的转换