你的FPGA复位用对了吗?

judy 在 周三, 01/31/2024 - 09:33 提交

今天我们就聊一聊FPGA复位应该如何用?看看哪些信号需要复位?

今天我们就聊一聊FPGA复位应该如何用?看看哪些信号需要复位?

同TX链路一样,RX的复位模式也是包含两种操作,这部分设置都一样

无论是FPGA开发还是芯片开发,其中一个重要的环节就是复位设计,本文主要说明FPGA的复位设计

首先回想一下,在平常的设计中我们是不是经常采用同步复位或者异步复位的写法,这一写法似乎都已经形成了肌肉记忆----每次我们写always块的时候总是会对所有的寄存器写一个复位赋初值的语句。

针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步复位还是异步复位?比如针对输入的异步复位信号rst,使用本地时钟clk将其同步化以后得到一个新的复位信号sys_rst,当使用sys_rst时,是将sys_rst作为同步复位信号还是异步复位信号?

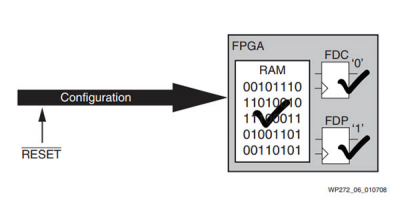

在Xilinx FPGA中实现的设计不需要插入全局复位网络。对于绝大多数设计,所有触发器和RAM的上电后的初始化状态比任何的逻辑复位都要全面,不需要为了仿真而插入复位,因为没有任何东西是未定义的

复位系统包括由硬件,看门狗定时器,JTAG控制器和软件产生的复位。Zynq-7000 SoC器件中的每个模块和系统都包含一个由复位系统驱动的复位。硬件复位由上电复位信号(PS_POR_B)和系统复位信号(PS_SRST_B)驱动。

本篇文章参考Xilinx White Paper:Get Smart About Reset: Think Local, Not Global。但如果认真看了Xilinx的White Paper,就会对复位有了新的认识。我们把White Paper的内容总结为下面4个问题

上电自复位对FPGA的稳定性及其重要,因为对于某些设计,上电之后需要进行一些状态寄存器的初始化,或者系统自己初始化都需要一个复位信号。在这里我就介绍一个比较好用的方法,大家一起学习一下

一开始接触到FPGA,肯定都知道”复位“,即简单又复杂。简单是因为初学时,只需要按照固定的套路——按键开关复位,见寄存器就先低电平复位一次,这样一般情况可以解决99%的问题,甚至简单的设计,就不可能有问题。复杂是因为复位本身是对大规模的硬件单元进行一种操作,必须要结核底层的设计来考虑问题