在 Vivado 中使用 HLS 创建的IP

judy 在 周四, 09/22/2022 - 09:44 提交

在本实践中,我们将实际实现 HLS 组件作为 FPGA 设计的一部分

在本实践中,我们将实际实现 HLS 组件作为 FPGA 设计的一部分

Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

在HLS中使用ap_fixed数据类型,可以结合硬件特性,很好的控制位宽

本文通过例子中来解释for循环中的基本概念

最近,在ACM的FPGA 2022会议上发表了一篇题为“RapidStream: FPGA HLS设计的并行物理实现”的论文,论文中描述了一种非常有趣的方法,通过FPGA设计软件推动HLS设计更快地运行在多核处理器上。

如果我需要修改HLS生成的RTL代码来验证一些问题,我该怎么做?

为了推断UltraRAM,你需要在所需的内部阵列上使用一个资源指令。

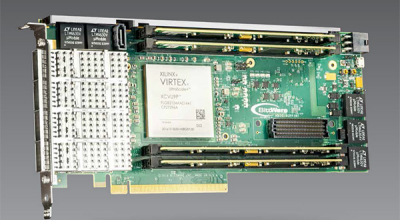

BittWare的SmartNIC Shell和BittWare的Loopback Example的功能之一是一个数据包解析器/分类器,它可以从数据包中提取协议字段。通过这篇白皮书,我们不仅要描述我们的Parser,还要解释如何使用HLS来构建和配置它,从而获得比使用P4语言更好的实现。

大多数FPGA程序员认为,高级工具总是发出更大的比特流,作为提高生产率的"成本"。 但事实总是如此吗?在本文中,我们展示了一个真实的例子