智多晶PLL IP动态相位调整

judy 在 周二, 04/09/2024 - 16:46 提交

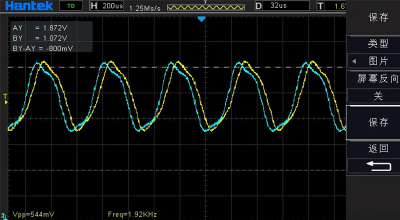

在FPGA中,动态相位调整(DPA)主要实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的。

在FPGA中,动态相位调整(DPA)主要实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的。

实验Vivado工程为“lvds_lcd”。本章介绍lvds lcd液晶屏的color bar显示。

信号链是连接真实世界和数字世界的桥梁

LVDS是一种满足当今高性能数据传输应用的新型技术

我们在设计外设和Xilinx 7系列FPGA互联时,经常会用到LVDS接口。如何正确的保证器件之间的互联呢?本博文整理了Xilinx官方相关技术问答

LVDS是一种低摆幅的差分信号技术,使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

很多工程师在使用Xilinx开发板时都注意到了一个问题,就是开发板中将LVDS的时钟输入(1.8V电平)连接到了VCCO=2.5V或者3.3V的Bank上,于是产生了关于FPGA引脚与LVDS(以及LVDS-33,LVDS-25)信号相连时兼容性的问题,该专题就解决一下这类问题。

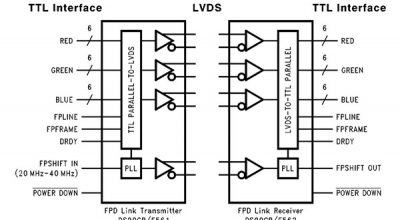

本文介绍两种LVDS数传接口:GMSL和FPD Link,这两种接口在汽车视频传输方面的应用是比较广泛的,尤其是Camera和处理器之间的链路,通过STP或者同轴电缆能使整个链路达到15m。

1、FPD Link