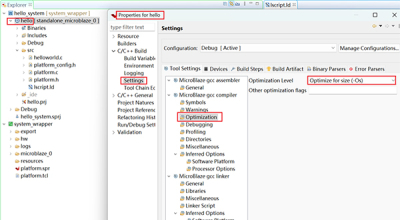

AMD FPGA的MicroBlaze固化流程

judy 在 周五, 03/22/2024 - 17:15 提交

MicroBlaze的易用性使得其开发如AMD其它嵌入式SoC FPGA一样简单

MicroBlaze的易用性使得其开发如AMD其它嵌入式SoC FPGA一样简单

在Block Design中查找IP时输入Microblaze,就会发现下面几种IP

PetaLinux编译Microblaze的U-Boot时,遇到下列错误

通过XTmrCtr_GetValue获取时间戳,是以时钟周期为单位的

使用手上现有的MicroBlaze工程,顺手测试了MicroBlaze的DMIPS数据

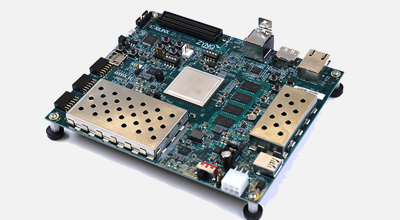

探讨如何在 Zynq UltraScale ZCU104 开发板上通过 PSU DDR 执行 MicroBlaze 应用

MicroBlaze 软核嵌入式处理器是高度可定制的 IP 核,支持 70 多个配置选项

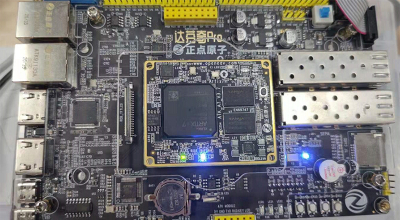

本节介绍最简单的实验工程,用串口打印helloworld。

本文介绍了当MicroBlaze包含在DFX可重构模块(RM)内时,更新MicroBlaze Block RAM的内容。

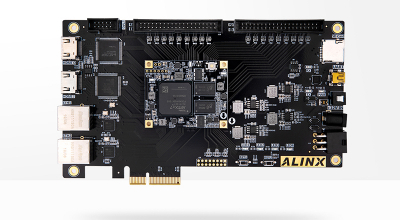

Xilinx FPGA MicroBlaze使用AXI 1G/2.5G Ethernet Subsystem(= Tri Mode Ethernet MAC + AXI Ethernet Buffer)以太网IP核驱动RTL8211FD千兆网口,并使用lwip2.1.2协议栈建立http服务器,支持IPv6