AMBA AHB总线

judy 在 周四, 01/04/2024 - 15:06 提交

本篇将带大家认识一下使用SystemVerilog描述的代码示例中的AHB总线信号接口以及工作时序。

本篇将带大家认识一下使用SystemVerilog描述的代码示例中的AHB总线信号接口以及工作时序。

今天给大家推荐下ARM自家所推出的BP063 AMBA4 SVA组件

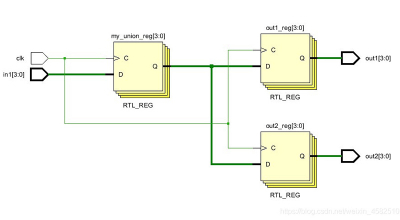

SystemVerilog 中新增了一种数据类型,即联合体。联合体支持您以多种不同方式来引用数据中的某一部分。本文将介绍联合体的使用方式以及综合工具针对联合体的处理方式。

FPGA工程师们应该都会吐槽Verilog的语法,相当的不友好,尤其是对于有很多接口的模块,像AXI4/AXI-Lite这种常用的总线接口,动不动就好几十根线,写起来是相当费劲。当然现在Xilinx推荐使用纯bd文件的方式来设计FPGA,这样HDL代码就会少了很多

FPGA工程师们应该都会吐槽Verilog的语法,相当的不友好,尤其是对于有很多接口的模块,像AXI4/AXI-Lite这种常用的总线接口,动不动就好几十根线,写起来是相当费劲。当然现在Xilinx推荐使用纯bd文件的方式来设计FPGA,这样HDL代码就会少了很多。但我们大多数的工程还是无法避免使用HDL来连接两个module

SystemVerilog 接口的开发旨在让设计中层级之间的连接变得更加轻松容易。 您可以把这类接口看作是多个模块共有的引脚集合。与必须在每个模块上定义多个引脚不同的是,您只需在接口中对引脚定义一次,之后只需在模块上定义接口即可。 如果稍后接口中涉及的信号被更改,则仅需更改接口即可