五项功能可提升边缘端嵌入式 AI 性能

judy 在 周三, 04/24/2024 - 09:51 提交

AI 驱动型系统正催生指数级算力需求,使得在紧凑的空间和功率限制内设计嵌入式应用变得更具挑战性。设计人员需要支持嵌入式 AI 系统中的所有计算阶段

AI 驱动型系统正催生指数级算力需求,使得在紧凑的空间和功率限制内设计嵌入式应用变得更具挑战性。设计人员需要支持嵌入式 AI 系统中的所有计算阶段

使用IBERT测试误码率和眼图必须有个收发环通的硬件,开发板上有2个SFP光纤接口,本实验把2个光接口收发两两连接,形成2个收发环通链路。

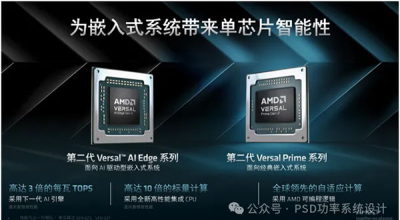

AMD 第二代 Versal AI Edge 系列和第二代 Versal Prime 系列自适应 SoC 为 AI 驱动和经典的嵌入式系统提供了单芯片智能性实现性能

继第一代Versal™ AI Edge自适应SoC之后,AMD又发布了第二代Versal™自适应SoC,为边缘计算打开了方便之门

有很多文档都描述了AI Engine的架构和性能参数,但是看完这些后,现实中遇到的问题最多的是这个AI Engine到底怎么用

系统看门狗定时器(System WatchDog Timer)通常用于嵌入式系统,可以有效的防止软件错误、系统死锁、篡改以及意外行为

第二代 Versal 系列产品组合中首批器件借助下一代 AI 引擎将每瓦 TOPS 提升至高 3 倍,同时将基于 CPU 的标量算力较之第一代提升至高 10 倍

实验Vivado工程为“lvds_lcd”。本章介绍lvds lcd液晶屏的color bar显示。

在非常多的客户应用工程中,都会用到DDR4/LPDDR4来存取大容量数据

本实验通过PL端Verilog代码直接读写ddr4,主要了解NoC的配置方法