采用 Simulink 和 AMD 赛灵思的 Vivado Simulator 开展 FPGA/SoC 早期设计验证

judy 在 周五, 10/21/2022 - 09:54 提交

本研讨会将演示如何使用可编程逻辑和 AI 引擎阵列功能对设计开展早期功能验证。

本研讨会将演示如何使用可编程逻辑和 AI 引擎阵列功能对设计开展早期功能验证。

本文描述在 Versal® ACAP 中实现电源排序的各种方法。

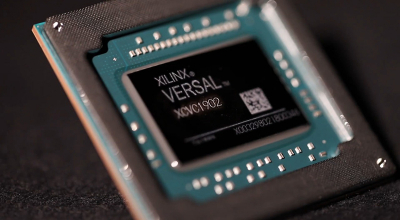

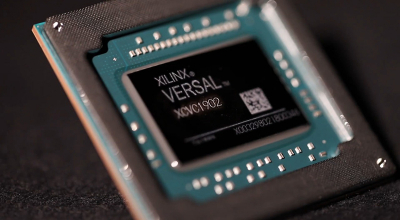

在 AMD,我们对 Versal® ACAP 所搭载的 AI 引擎技术感到兴奋不已,因为在 AMD 和赛灵思服务的众多市场上,其对交付高性能自适应计算起到重要作用。

该视频展示了即将推出的业界首款 Versal HBM 设备的稳健性,并展示了 HBM 堆栈在芯片上的高带宽利用率。

对于任何一项设计,要想尽可能实现最低的功率包络,都需要在设计周期早期准确估算功耗。早期估算有助于选择合适的器件、充分发挥架构优势、更改设计拓扑,以及使用不同 IP 块。在设计阶段早期妥善权衡取舍,可以帮助用户在满足规格要求的同时,将自身产品更快速推向市场。本文档旨在介绍如何根据 Versal™ ACAP 架构的描述来使用 Xilinx Power Estimator (XPE)。

欢迎参加Xilinx官方授权培训提供商-依元素科技举办的在线培训活动,专注于Versal®ACAP平台开发!了解最新的 Xilinx Versal ACAP 平台及其组成模块,支持更灵活地实现系统加速;Versal独有的功能特性,如人工智能引擎(AIE)和片上网络(NoC),将在Vitis统一软件工具流程中覆盖支持;

了解Versal™ ACAP的系统级优势以及与基于可编程逻辑的竞争器件的比较性能。

赛灵思 Versal™ 自适应计算加速平台 (ACAP) 设计方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。鉴于这些设计的规模与复杂性,因此必须通过执行特定步骤与设计任务才能确保设计每个阶段都能成功完成。遵循这些步骤和最佳实践进行操作,这将有助于以尽可能最快且最高效的方式实现期望的设计目标。

靠近模拟-数字边界边缘节点的位置对真实环境的即时响应受高度重视,众多市场领域存在迫切需求。Versal™ ACAP 产品组合 AI Edge 系列则应运而生,作为一种领域专用架构 (DSA),有效满足 7nm 芯片工艺系统提出的严苛要求。

Xilinx 的 16nm FPGA、SoC 和 7nm Versal™ ACAP 以硬化模块及软 IP 形式提供多种架构组件,这使得它们成了设计新一代安全设备的理想之选。这些 IP 包括高速串行解串器和多速率接口 IP,例如硬化 MAC、PCIe® 接口和内存控制器等。此外,Xilinx 器件还可提供业界一流的最新内存架构,其可为流程分类提供软搜索 IP,因此最适合网络安全与防火墙应用。