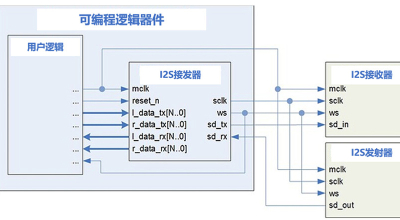

I2S 收发器 ( VHDL ) 设计实现

judy 在 周四, 03/14/2024 - 15:46 提交

这里详细介绍了一个主 I2S 收发器组件用于FPGAs,以 VHDL 编写

这里详细介绍了一个主 I2S 收发器组件用于FPGAs,以 VHDL 编写

VHDL是一门强大的硬件描述语言,能够帮助工程师们进行数字电路的设计和描述

我在 Vivado 中有个 VHDL 项目。 UG900 用户指南指出: “后综合和后实现时序仿真仅就 Verilog 提供支持。不支持 VHDL 时序仿真。” 这是否意味着我不能在 VHDL 项目中运行时序仿真? 该项目有没有运行时序仿真的办法?

Verilog语言和VHDL语言是两种不同的硬件描述语言,但并非所有人都同时精通两种语言,所以在某些时候,需要把Verilog代码转换为VHDL代码。本文以通用的XHDL工具为例对Verilog转换到VHDL过程中存在的问题进行了总结

VHDL 的一个强大功能是用库来组织 RTL 的不同部分。 通过使用库,不同的设计人员可以做这个工程中自己负责的那部分工作,而不必担心会在命名方面与其他设计师发生冲突。在例化期间,这可以通过手动指定要使用的库或者通过配置语句来完成。

课程对象

希望有效利用 VHDL 进行数字设计的建模、设计和综合的工程师

必备条件

数字设计的基本知识