Vitis 2020.1 - PetaLinux rootfs 中 Vitis 2020.1 的软件包管理具有不正确的提要链接

judy 在 周二, 07/05/2022 - 09:17 提交

在(UG1393) Vitis ... “ PetaLinuxrootfs 中的软件包管理”下的应用程序加速开发中,它描述了 Vitis 2020.1 版本的新软件包管理功能。

在(UG1393) Vitis ... “ PetaLinuxrootfs 中的软件包管理”下的应用程序加速开发中,它描述了 Vitis 2020.1 版本的新软件包管理功能。

如图所示, 源文件目录中haha文件夹下有一个hoho.h头文件。本来要包含这个头文件应该写成#include "haha/hoho.h"的,但是如果写成#include

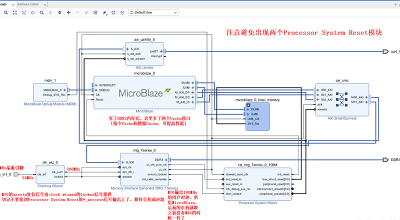

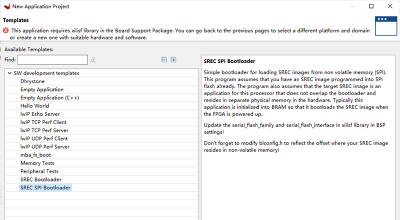

添加了DDR3内存以后,程序既可以运行在BRAM里面,也可以运行在DDR3内存里面。但如果运行在DDR3内存里面,固化起来会比较麻烦,需要借助SREC SPI Bootloader。

Xilinx Vitis 2020.1里面运行C程序时提示找不到microblaze_0

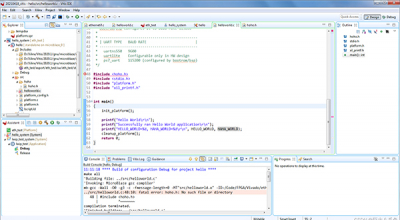

在Vitis里面创建了一个LwIP工程,调试的时候发现,在BRAM里面运行正常,但如果改到DDR3内存里面运行,启动时就会卡死在sleep函数上。于是建立了一个Hello World工程来检查,代码如下:

本教程以米联客XC7A35T FGG484-2开发板为例,详细讲解一下用Xilinx Vivado 2020.1创建MicroBlaze软核工程,然后再用Xilinx Vitis 2020.1建立Hello World C程序工程的完整操作步骤。

FPGA的型号为XC7A35TFGG484-2,开发板用的是米联客的。主程序hello_world运行于外部DDR3内存,SREC SPI Bootloader运行于FPGA片内BRAM。

修改了代码后编译工程,有时会因为BRAM空间不足而编译失败,出现下面的错误提示,这时,需要回到Vivado工程里面,在Block Design中将分配的BRAM空间大小改大。具体方法如下。

在BSP设置中,手动添加xilisf库的引用。首先,在Platform工程(这里是microblaze_test)上点击鼠标右键,选择“Open Platform Editor”命令。在Board Support Package里面,点击Modify BSP Settings按钮,勾选xilisf复选框,然后点击OK。

Vitis™统一软件平台是一种新的工具,它将Xilinx®软件开发的所有方面结合到一个统一的环境中。适合从边缘到云的所有开发者。Vitis 统一软件平台 2020.1 现已推出下载