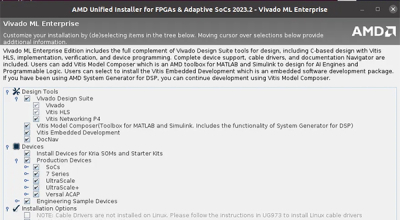

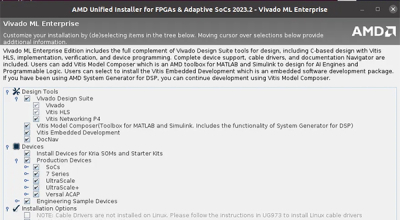

安装过程需要277GB的Vivado各个模块分别需要多大空间

judy 在 周五, 04/19/2024 - 09:57 提交

这篇文章我们看下Vivado的安装包中,到底哪些东西最占空间?

这篇文章我们看下Vivado的安装包中,到底哪些东西最占空间?

本文将详细介绍vivado仿真功能,包括如何使用、测试激励文件的撰写,以及如何调用第三方仿真测试软件。

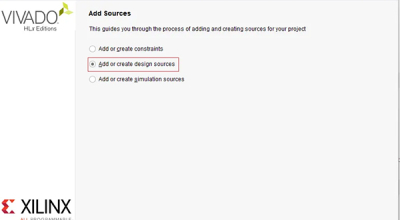

本文将详细介绍vivado添加或新建约束文件步骤和方法。

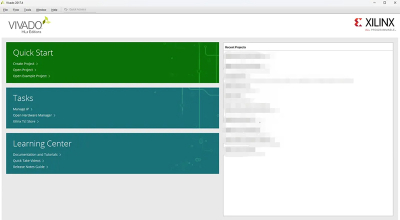

本文将详细介绍Vivado软件的使用方法,帮助初学者快速掌握AMD FPGA开发

本系列将详细介绍Vivado软件的使用方法,帮助初学者快速掌握AMD(Xilinx) FPGA开发。

如何在导入Block Design后,也一样实现聚合在一起?

本文将详细介绍SRL_STYLE的工作原理、可选值及其在实际设计中的应用代码示例。

在vivado中IP有两种综合方式“Global”和“out of context”

有时候我们想生成一个网表文件,但vivado默认是会生成一个dcp的文件

本文详细描述了 UNIMACRO 库。