Vivado® ML Editions 2022.2 最新更新

judy 在 周四, 11/03/2022 - 14:46 提交

AMD XILINX 近期全新推出了 Vivado® ML Editions 2022.2 版给工具集带来了多项重大改进与增强功能。

AMD XILINX 近期全新推出了 Vivado® ML Editions 2022.2 版给工具集带来了多项重大改进与增强功能。

Vivado® ML 2022.1 在 Vivado ML 标准安装中可支持 Versal Premium VP1202、VP1502、VP1702 和 VP1802 器件。

2021.2 的新增功能:全新器件支持:Artix® UltraScale+™: XCAU20P 和 XCAU25P;改进的智能设计运行以实现按钮时序收敛;Vivado® 中提供了全新的示例设计;增强高层次综合流的易用性

长期以来,EDA 面临着各种挑战:器件数量越来越多、设计越来越复杂。尽管摩尔定律逐步放缓,但在过去 20 多年间,FPGA 晶体管数量呈现的指数级增长丝毫未减。赛灵思利用堆叠硅片互联等技术,在异构集成方面取得了领先地位,同时还增加了 ARM 处理器子系统、AI 引擎或众多连接块

本文描述了两个ML建模应用,用于提高Vivado® ML版中时序延迟和路由拥塞估计的准确性。

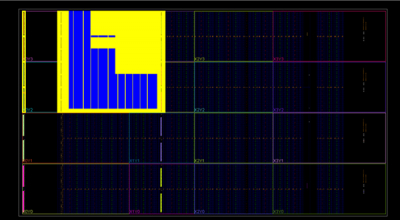

了解 Xilinx 如何通过 Vivado ML 中的动态可重配置功能助力实现资源的高效利用。

本文描述如何使用 Dynamic Function eXchange 灵活高效地使用硬件资源来动态更新已部署的系统。包括对技术历史的回顾。

赛灵思近日宣布推出 Vivado® ML 版,这是业内首个基于机器学习(ML )优化算法以及先进的面向团队协作的设计流程打造的 FPGA EDA 工具套件,可以显著节省设计时间与成本,与目前的 Vivado HLx 版本相比,Vivado ML 版将复杂设计的编译时间缩短了 5 倍,同时还提供了突破性的平均达 10% 的结果质量( QoR )提升。

Vivado ML 版支持基于机器学习的算法以加速设计收敛。该技术具备基于机器学习的逻辑优化、延迟估算和智能设计运行,能够自动执行策略以减少时序收敛迭代,将复杂设计的编译时间缩短了 5 倍,同时还提供了突破性的平均达 10% 的结果质量提升

Xilinx推出具有突破性技术的 Vivado ML 以加速设计收敛并提升 QoR,以及先进的 DFX 功能,可实现时间计算的创新形式。