Vivado 部分重配置 (PR) 解决方案中使用了哪些类型的比特流?

judy 在 周一, 12/04/2023 - 14:38 提交

本文档为 7 系列和 UltraScale 器件的每种比特流类型定义了术语,并进行了详细说明

本文档为 7 系列和 UltraScale 器件的每种比特流类型定义了术语,并进行了详细说明

Ubantu系统中vivado安装及配置

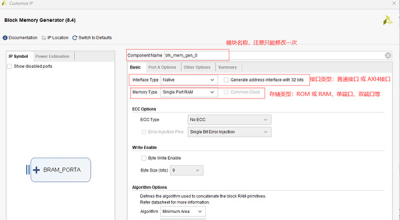

本文将详细介绍Vivado中BRAM IP的配置方式和使用技巧

我们在日常开发中经常使用sublime、vim、vs code等第三方的编辑器

详细介绍AMD最新发布的 Vivado Design Suite 2023.2

为硬件平台创建 PL IP 块、创建 PL 内核、功能仿真以及评估 AMD Vivado™ 时序收敛

本文将介绍如何在运行xx.xpr文件时,设置默认运行的版本

本文将详细介绍如何在Vivado中配置一个FIFO IP核

VGA作为视频接口,具有分辨率高、显示速度快、颜色丰富等优点