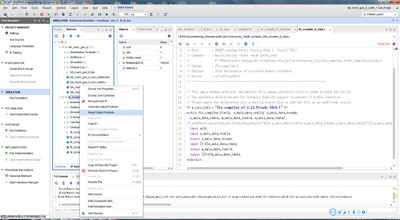

如何在Post Synthesis工程中加入 xci文件

judy 在 周四, 04/20/2023 - 16:12 提交

当使用第三方综合器比如 Synopsys® Synplify Pro或Mentor® Graphics Precision 来综合

当使用第三方综合器比如 Synopsys® Synplify Pro或Mentor® Graphics Precision 来综合

Aurora 协议是Xilinx公司针对高速传输开发的一种可裁剪的轻量级链路层协议

本文将介绍在Vivado中常用的TCL命令,并对其进行详细说明,并提供相应的操作示例。

使用“时钟校准去歪斜”时,在 Vivado 中会显示下列消息以指明是否启用该功能特性

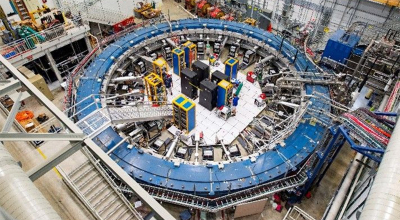

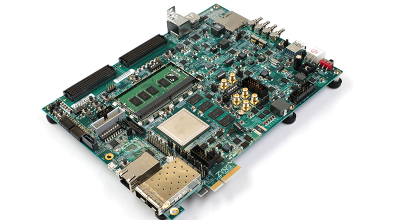

康奈尔大学在费米实验室合作开展Muon g-2实验,团队使用AMD的FPGA推动该研究领域最新成果

流水灯是大多数学习者接触到的第一个实验,也是非常经典的一个实验,在此,我们一起学习一下流水灯

根据自己vivado版本在branch中找到相同的版本

从xilinx官网下载了zcu106的例程文件,打开vivado下的TCL console窗口

在用vivado 生成IP核时,有两种综合方式:Global和out of context per IP。

在版本的Vivado 配套的 软件工具是 SDK ,当vivado中使用软核时候,需要将软核生成的elf文件