Vivado 用户指南:逻辑仿真

judy 在 周五, 03/10/2023 - 10:06 提交

本文提供了仿真进程以及 Vivado® Design Suite 中的仿真选项的概述

本文提供了仿真进程以及 Vivado® Design Suite 中的仿真选项的概述

FPGA的实现过程可以对综合后生成的网表进行逻辑综合优化、以及布局、布线方面的优化

在之前的学习当中,我们已经学习了Vivado的基本操作,接下来我们将继续学习软件的下板验证过程

本文介绍如何使用Vivado计算器件的封装延迟/封装飞行时间?

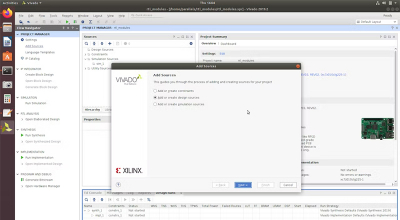

ADD 添加要合并的文件,第一个是fsbl的elf文件

Versal XPIO IOLOGIC 包含 IDDR、IFD、IDELAY、ODDR、OFD 和 ODELAY

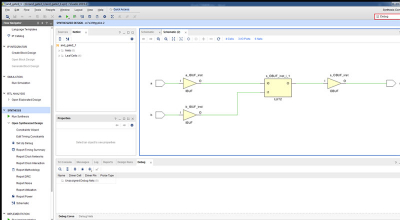

使用Vivado Block Design设计解决了项目继承性问题,但是还有个问题

本文介绍在使用源文件加密时的一些基本概念以及一些常见的问题

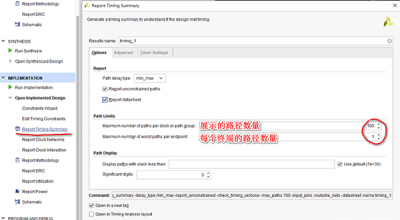

今天就通过一个简单的工程来看下如何在vivado软件中查看时序报告

在设计过程中,各个阶段的生成的文件都是.dcp,Vivado使用的是通用的模型贯穿在设计。