Vitis 库流程 - 在 Zynq 裸机设计中使用视觉库 L1 remap 函数的示例

judy 在 周一, 07/31/2023 - 11:31 提交

本文演示如何在 Zynq 设计中使用 Vitis 视觉库函数 (remap) 作为 HLS IP

本文演示如何在 Zynq 设计中使用 Vitis 视觉库函数 (remap) 作为 HLS IP

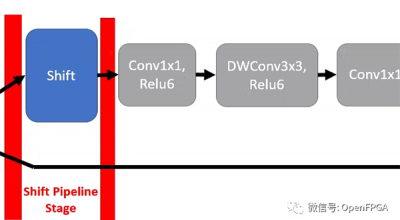

在这个项目中,将在线和离线 TSM 网络部署到 FPGA,通过 2D CNN 执行视频理解任务

探讨如何在 Zynq UltraScale ZCU104 开发板上通过 PSU DDR 执行 MicroBlaze 应用

根据自己vivado版本在branch中找到相同的版本

本文将探讨如何以 Zynq UltraScale 器件上的 IP 核为目标,使用 Python 来创建一些强大的应用和实用工具。

Zynq UltraScale+ MPSoC EV系列含有大量的视频输入接口,接入的视频流经过PL侧的逻辑处理后,通过USB3.0实现UVC输出各种高分辨率、高帧率、特殊格式的视频流

将面向专门用于卷积神经网络的可编程引擎DPU,并基于边缘端MPSOC器件(以官方ZCU104平台为例),引领开发者快速搭建基于Vitis AI的DPU开发环境

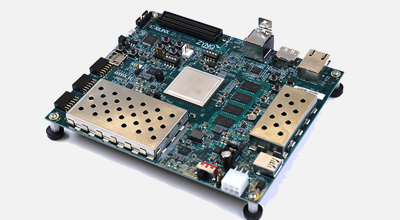

ZCU104 开发板基于Xilinx 公司Zynq UltraScale +XCZU7EV-2FFVC1156 MPSoC器件设计,支持嵌入式视觉使用案例的许多常见外设及接口

学习如何在 ZCU104 评估板上使用 VCU、DPU 和 PL 来构建和运行视频分析示例应用。

Xilinx 器件及 Vitis/Vitis AI 解决方案可为众多应用加速,包括视频处理、图像预处理、AI 推断以及内存带宽优化等。在本视频中,我们将演示如何使用 Xilinx ZCU104 开发人体检测应用。我们不仅将展示 Vitis AI 堆栈如何实现高速度、高精度和高性能,而且还将展示如何使用 Vitis HLS 库、DRM 以及 V4L2 等工具实现进一步优化。