【视频】利用 Zynq-7000 SoC 实现针对 DSP 功能的软件加速

judy 在 周五, 11/16/2018 - 14:21 提交

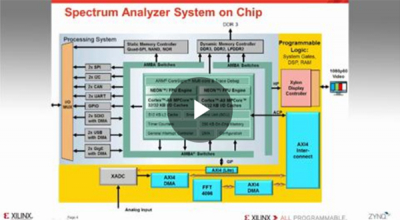

本演示介绍了 Zynq-7000 SoC 及其利用 NEON 引擎或硬件加速功能实现软件加速的能力。敬请查看 Zynq-7000 SoC 在面向数据采集和加速数字信号处理 (DSP) 的单芯片参考设计中的灵活性优势,其不仅可对软件进行加速,还能充分利用处理器和可编程逻辑之间的低延迟和高性能数据传送功能。

本演示介绍了 Zynq-7000 SoC 及其利用 NEON 引擎或硬件加速功能实现软件加速的能力。敬请查看 Zynq-7000 SoC 在面向数据采集和加速数字信号处理 (DSP) 的单芯片参考设计中的灵活性优势,其不仅可对软件进行加速,还能充分利用处理器和可编程逻辑之间的低延迟和高性能数据传送功能。

前言:

前面我们都是使用JTAG方式下载比特流文件,然后下载elf文件,最后点击Run as或者Debug as来运行程序。JTAG方式是通过tcl脚本来初始化PS,然后用JTAG收发信息,优点是可以在线调试,缺点是断电后程序就丢失了。为了解决程序丢失的问题,可以制作镜像文件烧写到sd卡或者flash中,上电即可加载程序。

前言:

ZYNQ 7000有三种GPIO:MIO,EMIO,AXI_GPIO

MIO是固定管脚的,属于PS,使用时不消耗PL资源;EMIO通过PL扩展,使用时需要分配管脚,使用时消耗PL管脚资源;AXI_GPIO是封装好的IP核,PS通过M_AXI_GPIO接口控制PL部分实现IO,使用时消耗管脚资源和逻辑资源。

前言:

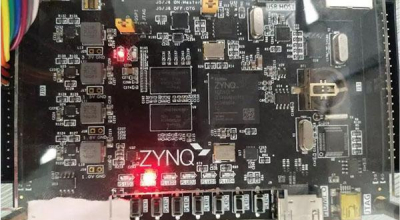

使用的板子是zc702。用Vivado的IP核搭建最小系统,包括ARM核(CPU xc7z020),DDR3(4×256M),一个UART串口(Mini USB转串口),纯PS,通过串口打印出HelloWorld,工程虽小,五脏俱全,算是一种朝圣。配置要和板子对应,大家注意修改。

操作步骤:

硬件部分

前言:

偶数分频容易得到:N倍偶数分频,可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去。

奇数分频如何得到呢?

第一部分 奇数分频

奇数分频方法:

作者:OpenSLee,来源:FPGA开源工作室

1 背景知识

在肤色识别算法中,常用的颜色空间为Ycbcr,Y代表亮度,cb代表蓝色分量,cr代表红色分量。

Avnet 展示了一款突出的集成型工业物联网系统,该系统在 Xilinx Zynq-7000 SoC 上集成机器视觉、马达控制和近场通信 (NFC),不仅可识别和挑选特定物品,随后还可根据用户选择将其放入正确的分配容器中。

作者:宋 凯,高 寒;来源:2018年电子技术应用第9期

作者: ChuanjieZhu

前言:

作者:OpenSLee

1 背景知识