上一篇咱们介绍了IO逻辑资源,本篇咱们来聊一聊高级的IO逻辑资源,即ISERDESE2模块和OSERDESE2模块。

所谓ISERDESE2模块,即Input serial-to-parallel converters。该模块的作用就是实现高速源同步输入数据的串并转换。

所谓OSERDESE2模块,即output parallel-to-serial converters。该模块的作用就是实现高速源同步输出数据的并串转换。

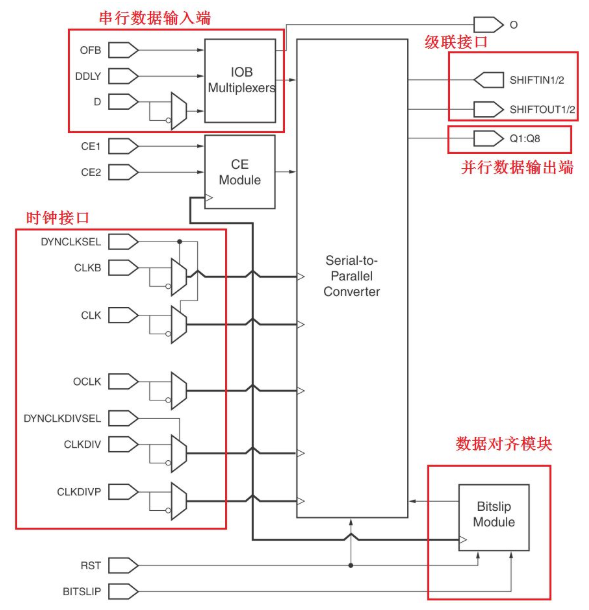

先说ISERDESE2。该模块接收外部输入FPGA的高速源同步串行信号,在FPGA内部将其转换为用户需要的并行数据信号。如图1所示为ISERDESE2的功能框图,咱们可以将按照功能分成5个部分:

1, 外部串行数据输入端

该部分接收外部输入的高速源同步数据,数据可以为SDR或者DDR。在SDR模式时,数据转换的位宽可以为2、3、4、5、6、7、8bit。在DDR模式时,数据转换位宽为4、6、8bit,当然如果是2个ISERDESE2级联使用,DDR模式可以支持10、14bit。

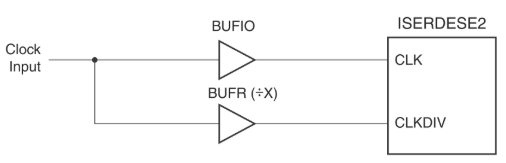

2, 时钟接口

该部分提供ISERDESE2工作的高速源同步串行时钟、并行数据获取时钟以及控制时钟。如图2所示为源同步时钟接入ISERDESE2的用法。

3, 并行数据输出端

该接口就不用多说了,就是最终咱们需要的并行数据。SDR模式下为2、3、4、5、6、7、8bit,DDR模式下为4、6、8、10、14bit。

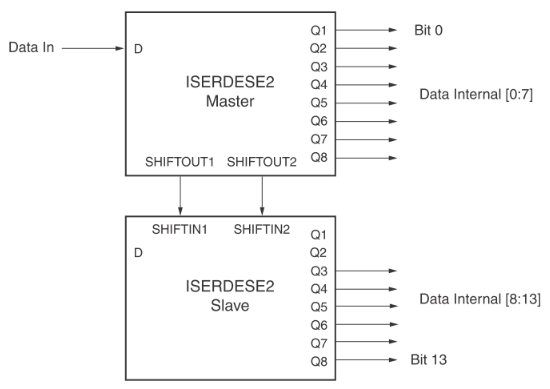

4, 级联接口

该接口是实现DDR模式下10bit、14bit位宽的关键接口,通过该接口与另外一个ISERDESE2级联,两者共同完成10bit、14bit数据的串并转换。如图3即为2个ISERDESE2的级联使用。

5, 数据对齐模块

该模块又称作Bitslip模块,用来实现并行数据的边界对齐。比如咱们外界串行输入的8bit的数据,经过串并转换后,能获取8bit的并行数据,但这并行数据可能存在前后8bit数据之间的错位,这是串并转换无法识别的,因此Bitslip就专门用来找到用户需要的并行数据边界。

图4给出了Bitslip是如何确定并行数据的边界:对于SDR模式,Bitslip使能1次,则数据会左移1次,对于8bit并行数据,移动8次完成一个循环,可以这样无止境的循环,直到找到用户定义的并行数据。对于DDR模式,Bitslip工作方式不同,Bitslip使能1次,数据会右移1次或者左移3次,两者交替进行,同样移动8次完成一个循环。

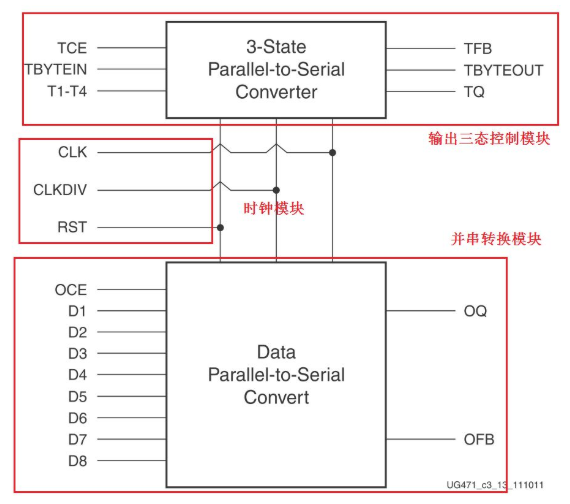

咱们再说OSERDESE2模块。该模块和ISERDESE2模块不同,少了Bitslip模块,多了一个三态控制模块,可以实现三态控制并串转换功能,数据的位宽和咱们介绍的ISERDESE2规则一样。如图5所示为其功能框图:

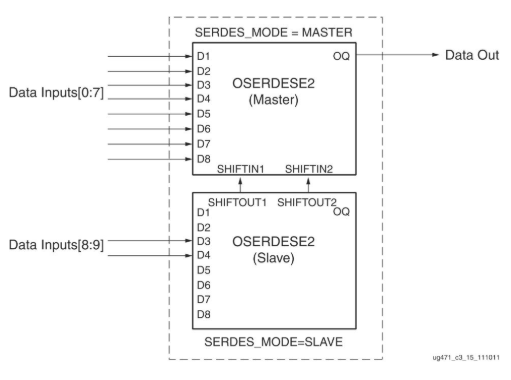

如图6所示为OSERDESE2的级联设计,实现10、14bit的并串转换功能:

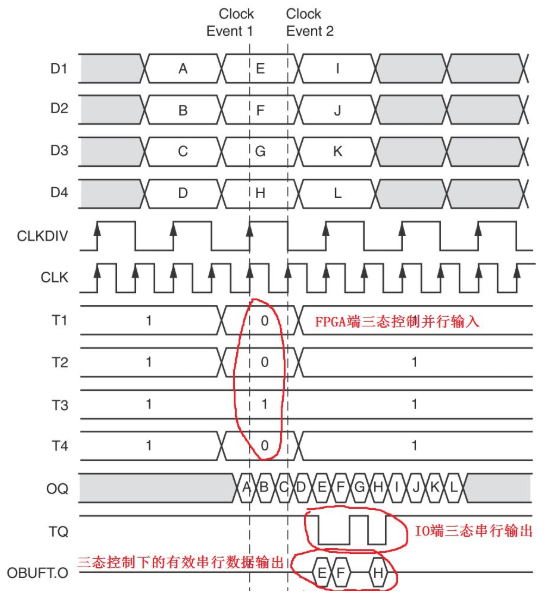

OSERDESE2除了多出了一个三态控制模块,其它和ISERDESE2基本一样,只是数据流反相操作,因此咱们这里主要看一下三态控制模块,该模块主要功能就是实现串行数据流的三态输出,图7给出了三态控制的详细时序结构,从图上我们可以看到,三态控制下,串行数据流有选择性的输出E、F、H,实现了输出串行数据的三态控制。

本篇咱们很简要的介绍完了ISERDESE2和OSERDESE2,大家了解了吗?当然如果要实际使用的话,咱们还得看看具体数据手册啦!在上篇咱们就说过了,IO部分是FPGA内最复杂的部分,也是设计起来最难的部分,要熟悉使用它,咱们还得下功夫钻研!

文章来源:XiaoQingCaiGeGe的博客

声明:本文由原创博主授权转发,如需转载请联系博主