作者:艮林子 校对:陆辉,本文转载自: FPGA技术江湖微信公众号

今天带来第五篇,介绍建立系统和Vitis IDE调试流程。后续还会带来详细的开发教程,敬请关注。话不多说,咱们就进入正题。

八、使用Vitis IDE

8.3 建立系统

构建系统时,最佳实践是使用Build Targets中描述的三个可用构建目标。每个构建目标在助手视图中以单独的构建配置表示。按以下顺序完成这些构建配置:

仿真软件:构建软件仿真(sw_emu),以确认主机程序和内核代码一起工作的算法功能。

仿真硬件:构建硬件仿真(hw_emu),以将内核编译为硬件描述语言(HDL),确认所生成逻辑的正确性,并评估其仿真性能。

系统:执行系统硬件构建(hw),以实现在目标平台上运行的应用程序。

在启动build命令之前,请配置每个构建配置,以确保其满足您的需求。选择特定的构建配置,然后单击“ 设置”图标以打开“构建配置设置”对话框。有关使用此对话框的更多信息,请参考《 Vitis Build配置设置》。

除了构建配置设置外,许多会影响您的应用程序的设置都包含在“硬件功能”中,可通过“ Vitis硬件功能设置”对话框访问。最好查看配置Vitis IDE中讨论的每个“设置”对话框。

在助手视图中,指定了构建配置的各种选项,您可以通过选择构建配置并单击“ 构建”( )按钮来启动构建过程。所述葡萄核心开发工具包使用,其产生的两个部分构建过程的FPGA二进制(.xclbin)用于硬件内核使用葡萄 编译器v++命令,并编译和使用该主机的程序代码链接g++的编译器。

)按钮来启动构建过程。所述葡萄核心开发工具包使用,其产生的两个部分构建过程的FPGA二进制(.xclbin)用于硬件内核使用葡萄 编译器v++命令,并编译和使用该主机的程序代码链接g++的编译器。

构建过程完成后,“助手”视图将显示特定的构建配置,并带有绿色的复选标记,以指示已成功构建它,如下图所示。您可以打开任何构建报告,例如硬件功能中的“编译摘要”或二进制容器中的“链接摘要”。在“助手”视图中右键单击报告,然后选择“ 在Vitis Analyzer中打开”。

构建完成后,您现在可以在特定构建配置提供的上下文中运行应用程序。例如,在Emulation-SW构建中行使宿主程序和FPGA二进制代码一起工作的C模型,或者在Emulation-HW构建中在仿真中查看宿主程序和RTL内核代码,或者在目标计算机上运行应用程序系统构建中的平台。

要从Vitis IDE中运行该应用程序,请选择构建配置,然后单击“ 运行”按钮()以启动默认运行配置。您也可以右键单击构建配置,然后使用“ 运行” 菜单选择特定的运行配置,或按照Vitis“运行配置设置”中的说明编辑运行配置。

8.3.1 Vitis IDE指导视图

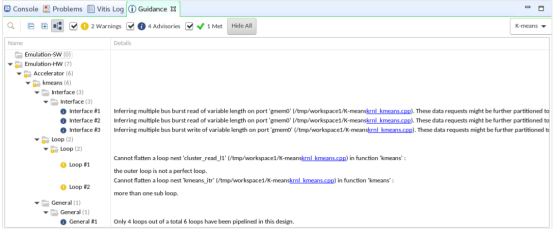

生成或运行特定的生成配置后,“控制台”视图的“引导”选项卡将显示与运行或生成过程相关的错误,警告和建议的列表。指导视图将自动填充并显示在控制台视图中的选项卡中。您可以查看指导消息,以进行代码或构建过程中可能需要的任何更改。

运行硬件仿真后,“指导”视图可能如下图所示。

为了简化对“指导”视图信息的排序,Vitis IDE允许您搜索和过滤“指导”视图以查找特定的指导规则条目。您可以折叠或展开树视图,甚至取消层次结构树表示,并可视化指导规则的精简表示。最后,您可以通过启用或禁用警告以及已满足的规则的显示来选择在“指导”视图中显示的内容,还可以根据消息的来源(例如构建和仿真)来限制特定的内容。

默认情况下,“指导”视图显示下拉菜单中所选项目的所有指导信息。要将内容限制为单独的构建或运行步骤,请执行以下操作:

1.选择窗口> 首选项

2.选择类别Guidance。

3.取消选择按项目分类的组指导规则检查

8.3.2 从Vitis IDE使用Vivado工具

Vitis核心开发工具包调用 Vivado设计套件在链接过程中自动运行RTL合成并产生FPGA二进制(xclbin)时实现。可以选择直接从Vitis IDE 中启动Vivado工具,以与项目进行交互以合成和实现FPGA二进制文件。可通过Xilinx > Vivado集成菜单访问以下三个命令,以支持从Vitis IDE 与Vivado工具进行交互:

打开Vivado项目:这将自动打开与系统构建配置关联的Vivado项目(.xpr)。为了使此功能起作用,您必须事先完成系统构建,以便存在用于构建的Vivado项目。

打开Vivado 项目将启动Vivado IDE,并打开实现设计检查点(DCP)文件以编辑该项目,从而使您可以更直接地管理综合和实现的结果。然后,您可以使用此工作的结果,通过使用Import Design Checkpoint 命令来生成FPGA二进制文件。

导入设计检查点:可让您指定一个Vivado设计检查点(DCP)文件,用作系统构建和生成FPGA二进制文件的基础。

导入Vivado设置:可以导入配置文件(如Vitis Compiler配置文件中所述),以在链接过程中使用。

在独立模式下使用Vivado IDE可以探索各种综合和实现选项,以进一步优化内核的性能和面积。还有其他选项可用于与FPGA构建过程进行交互。有关更多信息,请参见在Vivado工具中管理FPGA综合和实现结果。

8.4 Vitis IDE调试流程

Vitis IDE提供方便的调试功能。手动执行时,设置可执行文件进行调试需要很多步骤。使用调试流程时,Vitis IDE将自动处理这些步骤。

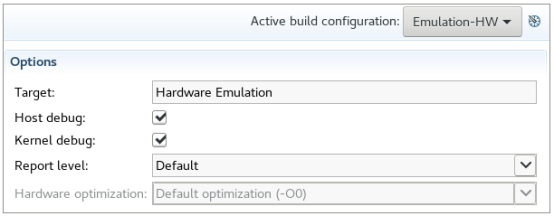

要准备可执行文件进行调试,必须更改构建配置以启用调试标志的应用。在Vitis IDE 的“项目编辑器”视图中设置这些选项。在“选项”部分中提供了两个复选框,用于“活动”构建配置。主机调试可在主机编译中启用调试结构。内核调试可启用内核调试。

还可以通过在“构建配置设置”对话框中启用调试功能,如Vitis“构建配置设置”所示,方法是在“助手”视图中选择构建配置,然后单击“ 设置”按钮。或者,您可以双击构建配置。出现了相同的两个复选框。虽然可以在所有目标上启用主机调试,但是仅软件仿真和硬件仿真构建目标才支持内核调试。

从Vitis IDE 运行GDB会话将完成所有必需的设置。它会自动管理用于硬件或软件仿真的环境设置。如xrt.ini File中所述,它配置Xilinx运行时(XRT)以确保在应用程序运行时提供调试支持,并管理执行主机代码,内核代码和调试服务器所需的不同控制台。

在设置好用于调试的构建配置之后,清理构建目录并重新构建应用程序,以确保该项目已准备好在GDB调试环境中运行。

要启动调试会话,请在“助手”视图中选择构建配置,然后单击“ 调试”( )按钮。在Vitis IDE中启动调试会话时,透视图将切换到“调试”透视图,该视图被配置为显示其他窗口,以管理不同的调试控制台和源代码窗口。

)按钮。在Vitis IDE中启动调试会话时,透视图将切换到“调试”透视图,该视图被配置为显示其他窗口,以管理不同的调试控制台和源代码窗口。

启动应用程序后,默认情况下,应用程序会main在主机代码中函数主体的开头立即停止。与任何GDB图形前端一样,您现在可以设置断点并检查主机代码中的变量。该葡萄 IDE能够在一个透明的方式加速内核实现同样的功能。有关更多信息,请参阅调试应用程序和内核。

本篇到此结束,下篇还会继续连载,欢迎大侠关注!