作者:张大侠 ,本文转载自:傅里叶的猫微信公众号

什么是ECO?ECO 指的是Engineering Change Order,即工程变更指令。目的是为了在设计的后期,快速灵活地做小范围修改,从而尽可能的保持已经验证的功能和时序。ECO 的叫法算是从IC 设计领域继承而来,其应用在FPGA设计上尚属首次,但这种做法其实在以往的FPGA 设计上已被广泛采用。

ECO在一些大的工程中是比较实用的,比如工程编好后,想将一个已有的信号连接到FPGA端口上观察,或者想增加Debug信号、修改寄存器初始值等,都可以直接对route之后的dcp进行修改,而不需要重新综合和布局布线。这样就大大缩减了调试时间。

本篇文章我们以Vivado的wave_gen工程为例,来看下如何通过ECO来增加一个LUT,并对内部信号实现取反的功能。

Vivado版本:2019.2

打开Vivado中的wage_gen的工程:

直接进行Run Implementation,在实现完成后,在Tcl Console中打开route之后的dcp文件。

cd [get_property directory [current_project ]] open_checkpoint ./project_1.runs/impl_1/wave_gen_routed.dcp

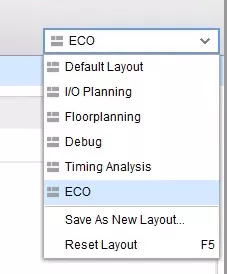

在新打开的Vivado窗口中,切换到ECO

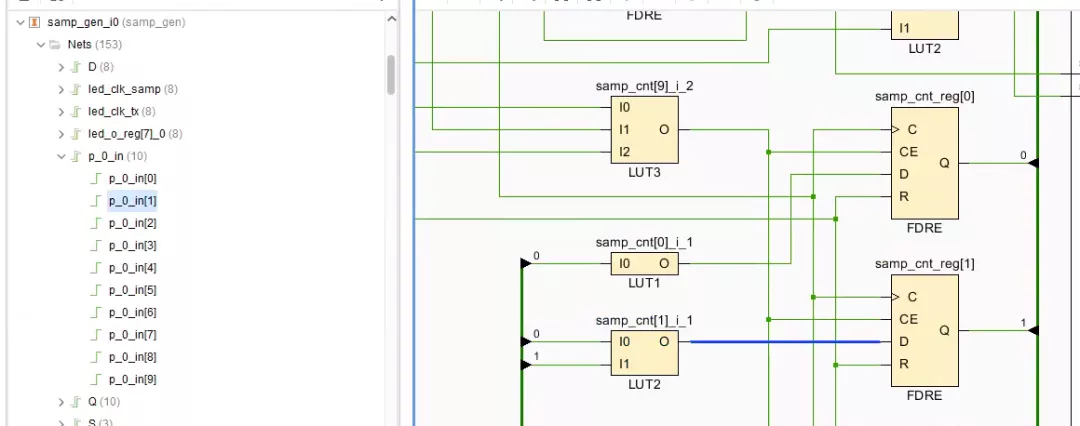

假设我们需要对samp_gen_i0/p_0_in[1]的net上增加一个取反的功能,即前面LUT2输出取反后再连接到后面FDRE的输入上。(请记住这个net的名字)

操作步骤如下:

选中FDRE的输入端D,并点击左边页面的Disconnect Net

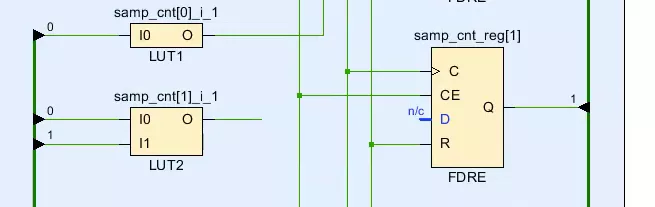

可以看到会变成下面的样子:

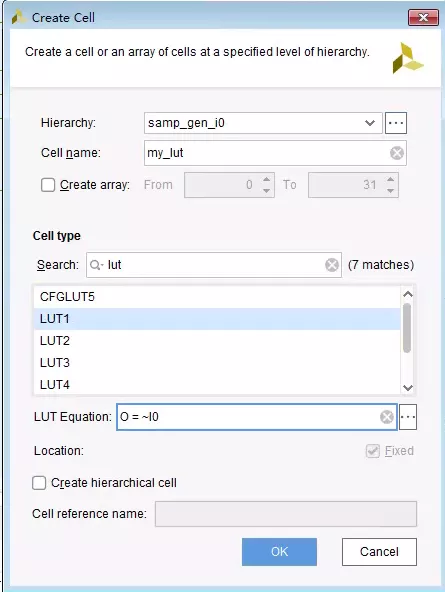

点击左边页面的Create Cell,设置如下:

点击OK后,就新建了一个Cell,但位置是随机上的,可以点击Zoom Fit之后找一下。

而且之前的Cell的位置也会发生变化,我们刚刚断开连接的samp_cnt[1]_i_1和samp_cnt_reg[1]的位置也变了,由于我们是图形化操作,所以同样需要找一下。

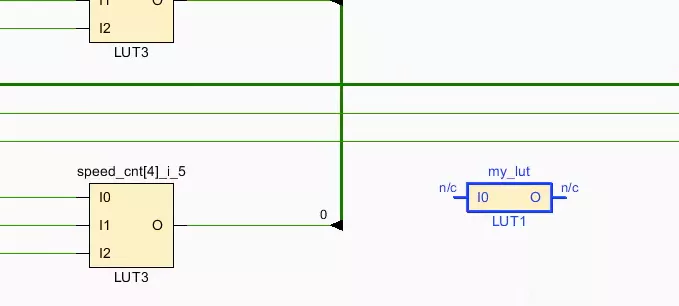

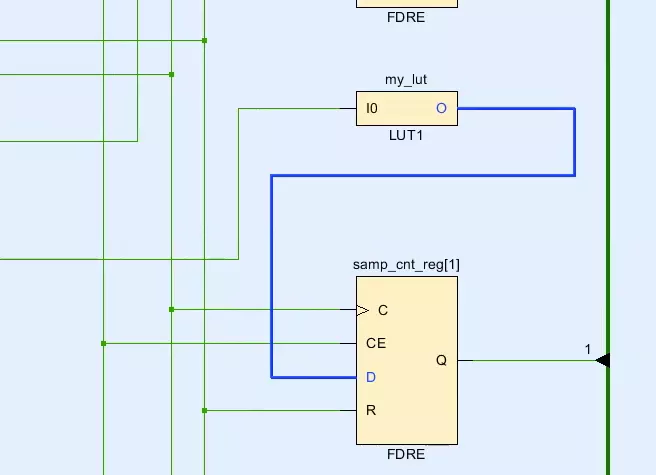

将my_lut的输入端连接到samp_gen_i0/p_0_in[1]上,也就是第一步中断开链接的net。操作方法就是同时选中my_lut的输入端口和samp_gen_i0/p_0_in[1],点击左边页面的Connect Net,就可以看到下面的连接完成的结果:

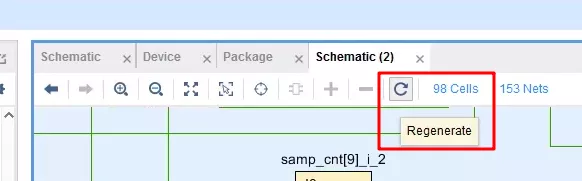

这个时候可以点一下Regenerate按钮,页面重新布局一下,可能使我们后面的操作更加方便。

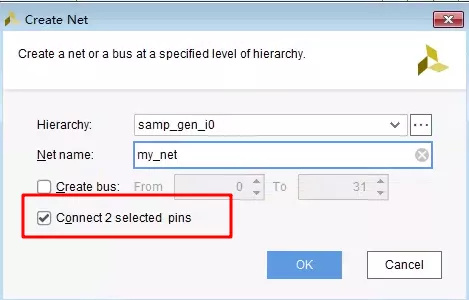

连接my_lut的输出到samp_cnt_reg[1]的输入,同时选中这两个pin,点击左边页面的Create Net,勾选Connect 2 selected pins

可以看到,这两个pin也连接到了一起

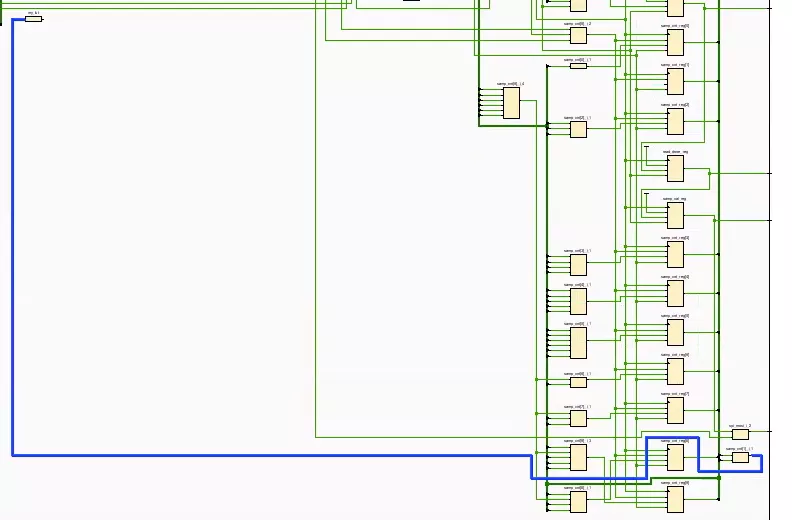

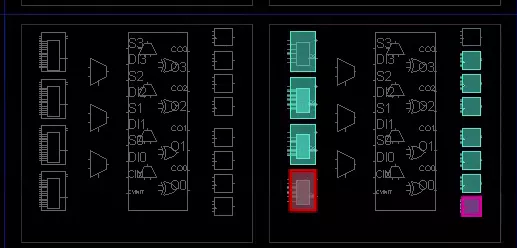

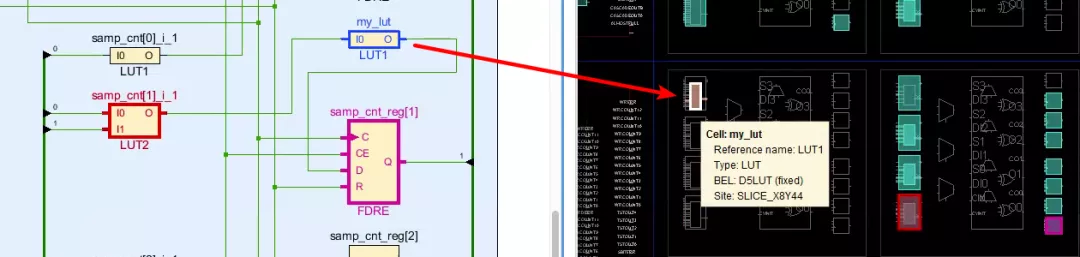

接下来是比较关键的一步--Place,要把我们新增加的LUT放到Device中。我们可以先把my_lut前后两个Cell都highlight一下,方便在Device窗口中观察。可以看到,这两个Cell放到了一个Slice中,而且这个Slice中的LUT已经被占满。

我们把my_lut放到同一个CLB的另外一个Slice中,直接在Schematic中选中my_lut,并拖拽至Device的LUT中。

到了这一步,ECO的操作就基本结束了。

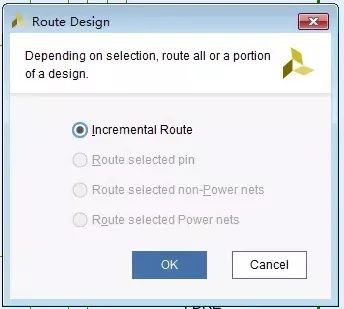

Route,直接点击左边页面的按钮即可,会弹出下面的窗口,意思是增量Route,只对我们刚刚修改的位置进行route。

Check ECO,直接点击按钮即可

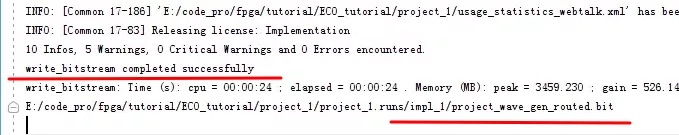

如果ECO Check没什么问题,就可以Generate Bitstream了。

到这里就完成了ECO的整个过程。

当然,整个过程都可以使用tcl来完成,我们后续再来演示。