本文转载自:巨大八爪鱼的博客

【错误提示】

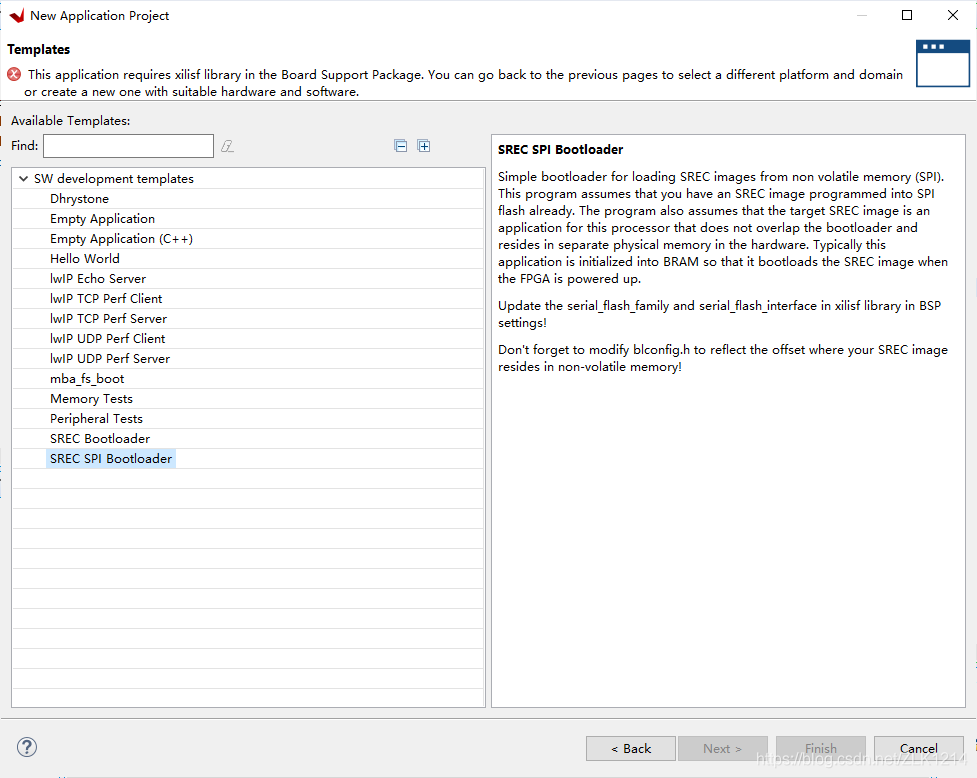

This application requires xilisf library in the Board Support Package. You can go back to the previous pages to select a different platform and domain or create a new one with suitable hardware and software.

【解决办法】

在BSP设置中,手动添加xilisf库的引用。

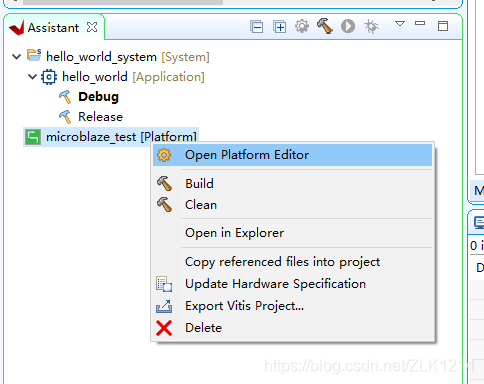

首先,在Platform工程(这里是microblaze_test)上点击鼠标右键,选择“Open Platform Editor”命令。

在Board Support Package里面,点击Modify BSP Settings按钮,勾选xilisf复选框,然后点击OK。

勾选后一定要记得Build一下Platform Project,不然设置不会生效!

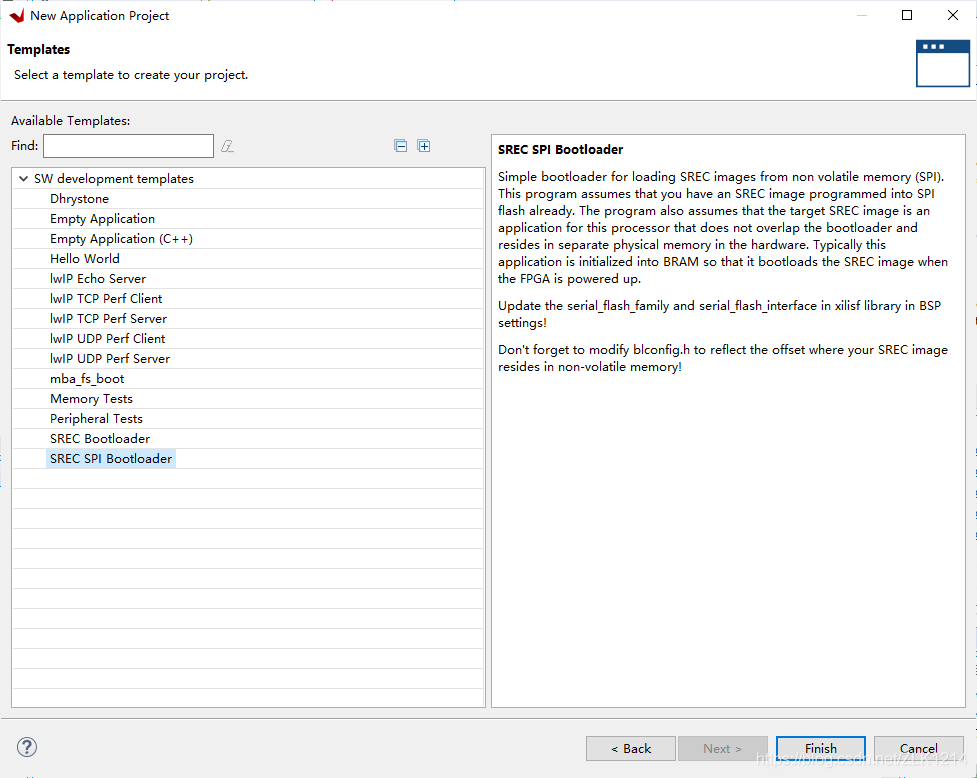

现在就可以成功创建SREC SPI Bootloader工程了:

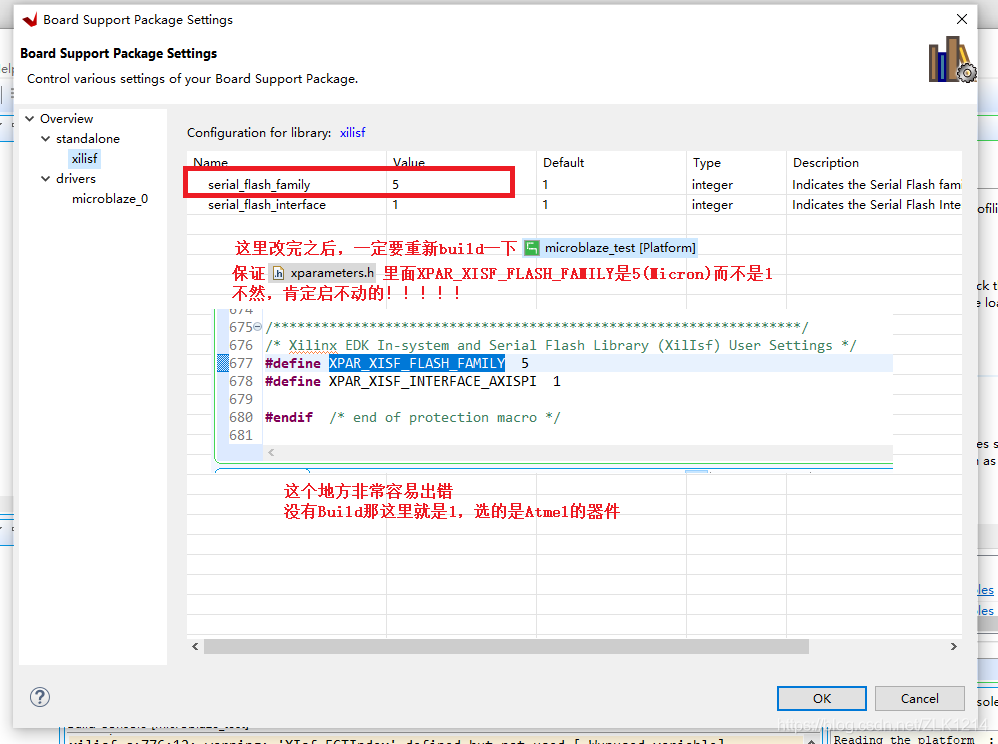

创建完工程后,我们要去修改serial_flash_family号。修改完之后,必须要再build一下platform工程,否则设置不会生效,xparameters.h里面的XPAR_XISF_FLASH_FAMILY还是1,Debug调试bootloader工程会发现他进入的是ATMEL的分支而出错。

改完之后编译SREC工程会发现编译不通过,提示BRAM空间不足:

'Invoking: MicroBlaze gcc linker'

mb-gcc -Wl,-T -Wl,../src/lscript.ld -LE:/fpga_projects/test4/microblaze_test/export/microblaze_test/sw/microblaze_test/standalone_domain/bsplib/lib -mlittle-endian -mcpu=v11.0 -mxl-soft-mul -Wl,--no-relax -Wl,--gc-sections -o "bootloader.elf" ./src/bootloader.o ./src/platform.o ./src/srec.o -Wl,--start-group,-lxil,-lgcc,-lc,--end-group -Wl,--start-group,-lxilisf,-lxil,-lgcc,-lc,--end-group

c:/xilinx/vitis/2020.1/gnu/microblaze/nt/x86_64-oesdk-mingw32/usr/bin/microblaze-xilinx-elf/../../libexec/microblaze-xilinx-elf/gcc/microblaze-xilinx-elf/9.2.0/real-ld.exe: bootloader.elf section `.stack' will not fit in region `microblaze_0_local_memory_ilmb_bram_if_cntlr_Mem_microblaze_0_local_memory_dlmb_bram_if_cntlr_Mem'

c:/xilinx/vitis/2020.1/gnu/microblaze/nt/x86_64-oesdk-mingw32/usr/bin/microblaze-xilinx-elf/../../libexec/microblaze-xilinx-elf/gcc/microblaze-xilinx-elf/9.2.0/real-ld.exe: region `microblaze_0_local_memory_ilmb_bram_if_cntlr_Mem_microblaze_0_local_memory_dlmb_bram_if_cntlr_Mem' overflowed by 744 bytes

collect2.exe: error: ld returned 1 exit status

'Finished building target: bootloader.elf'

这个时候要回到Vivado里面,把Microblaze的BRAM空间改大。具体修改方法请参阅:

https://blog.csdn.net/ZLK1214/article/details/111501773