本文转载自: 硬码农二毛哥

DDR接口信号

DDR接口信号分为DDR对外接口信号、用户应用接口信号和读写控制信号。对外接口信号直接与DDR芯片连接,用户应用接口信号为DDR控制器IP输出信号,通过用户控制接口信号生成控制DDR读写控制信号。

DDR 对外接口信号

对外接口信号直接与DDR芯片连接。

//ddr interface

.ddr3_addr (ddr3_addr), //ddr address

.ddr3_ba (ddr3_ba), //ddr bank address

.ddr3_cas_n (ddr3_cas_n), //ddr column address strobe

.ddr3_ck_n (ddr3_ck_n), //ddr clock enable

.ddr3_ck_p (ddr3_ck_p), //ddr positive clock

.ddr3_cke (ddr3_cke), //ddr negative clock

.ddr3_ras_n (ddr3_ras_n), //ddr row address strobe

.ddr3_we_n (ddr3_we_n), //ddr write enable

.ddr3_dq (ddr3_dq), //ddr data

.ddr3_dqs_n (ddr3_dqs_n), //ddr data positive clock

.ddr3_dqs_p (ddr3_dqs_p), //ddr data negative clock

.ddr3_reset_n (ddr3_reset_n),//ddr reset

.init_calib_complete (init_calib_complete),//ddr init done

.ddr3_cs_n (ddr3_cs_n), //ddr chip select

.ddr3_dm (ddr3_dm), //ddr data enable

.ddr3_odt (ddr3_odt) //ddr On-Die Termination

DDR 用户应用接口信号

用户应用接口信号,还是相对复杂,通过将用户应用接口信号转换成读写控制信号后,直接控制DDR读写。

.app_addr(app_addr),

.app_cmd(app_cmd),

.app_en(app_en),

.app_wdf_data(app_wdf_data),

.app_wdf_end(app_wdf_end),

.app_wdf_mask(app_wdf_mask),

.app_wdf_wren(app_wdf_wren),

.app_rd_data(app_rd_data),

.app_rd_data_end(app_rd_data_end),

.app_rd_data_valid(app_rd_data_valid),

.app_rdy(app_rdy),

.app_wdf_rdy(app_wdf_rdy),

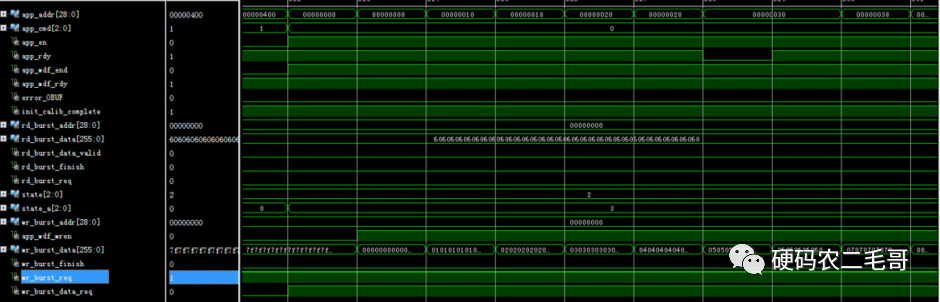

DDR写

wr_burst_req = 1 时,将app_en 置1,app_wdf_end置1

app_addr_r<= {wr_burst_addr,3'd0};//app数据位宽为256,ddr数据位宽为32,需要乘8

app_cmd_r <= 3'b000;

进入到写数据状态。

app_rdy为1时,app_addr_r <= app_addr_r + 'b1000;

会遇到app_rdy = 0 的情况,app_addr_r不增加。wr_addr_cnt用来计数突发长度128,也是在app_rdy为1时增加。

wr_burst_data_req为1时,wr_data_cnt增加,记录写入数据的个数,wr_data_cnt与wr_addr_cnt不一定相同,因为app_rdy在wr_burst_data_req =1时可能为0,此时wr_data_cn大于wr_addr_cnt。

wr_data_cnt等于突发长度128时

当wr_addr_cnt等于突发长度128时,将app_wdf_end_r<= 1'b0;app_en_r <= 1'b0;

判断app_wdf_rdy ==1 ,进入写完成状态。

在写完成状态,wr_burst_finish =1;

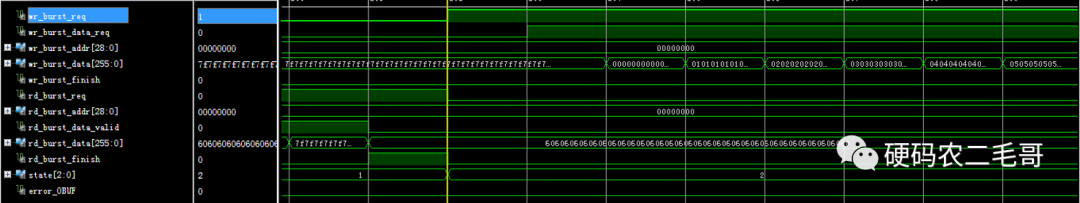

DDR读

rd_burst_req = 1时开始读,将app_cmd_r <= 3'b001;app_addr_r <= {rd_burst_addr,3'd0};

app_en_r <= 1'b1;进入1状态。app_rdy =1 时,app_addr_r <= app_addr_r + 8; rd_addr_cnt增加。app_rd_data_valid在1状态为1时,开始读出数据,rd_data_cnt记录读出数据个数。

由于从rd_burst_req 到app_rd_data_valid间隔时间较久,所以rd_addr_cnt计数快于rd_data_cnt,当rd_addr_cnt =128时,进入读等待状态,app_en_r <= 1'b0;

在读等待状态,rd_data_cnt =128时,进入读完成状态,读操作结束。

DDR 读写控制信号

写入数据的时候,只需要控制写请 求 信 号 wr_burst_req, 写长度 信号wr_burst_len , 写地址信号wr_burst_add 和写数据wr_burst_data。

读数据的时候,只需要控制读请求信号rd_burst_req, 读长度信号rd_burst_len , 读地址信号rd_burst_add, 读数 据有效信号rd_burst_data_valid 和读数据rd_burst_data。

//ddr read&write internal interface

.wr_burst_req (wr_burst_req), //ddr write request

.wr_burst_addr (wr_burst_addr), //ddr write address

.wr_burst_data_req (wr_burst_data_req), //ddr write data request

.wr_burst_data (wr_burst_data), //fifo 2 ddr data input

.wr_burst_finish (wr_burst_finish), //ddr write burst finish

.rd_burst_req (rd_burst_req), //ddr read request

.rd_burst_addr (rd_burst_addr), //ddr read address

.rd_burst_data_valid (rd_burst_data_valid), //ddr read data valid

.rd_burst_data (rd_burst_data), //ddr 2 fifo data input

.rd_burst_finish (rd_burst_finish), //ddr read burst finish

//burst length

.wr_burst_len (10'd100), //ddr write burst length

.rd_burst_len (10'd100), //ddr read burst length

DDR读写时序

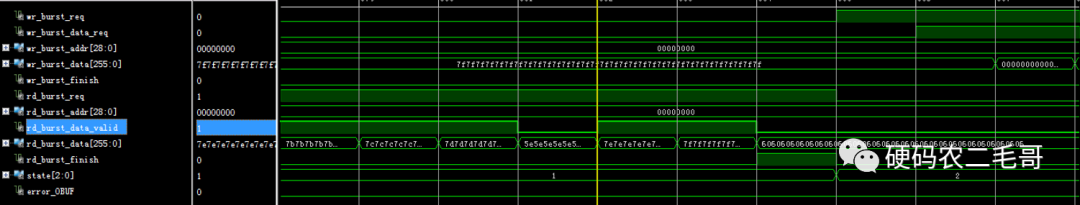

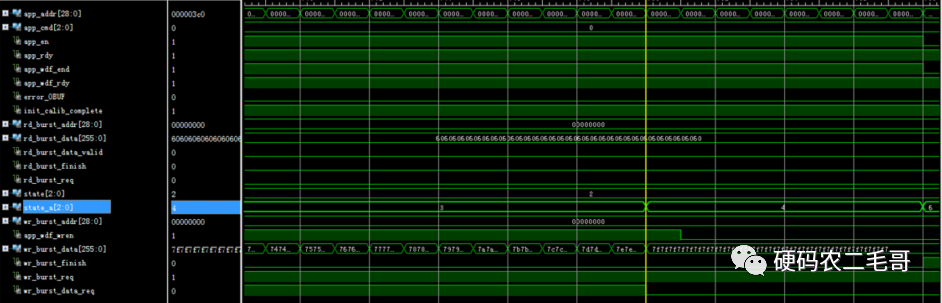

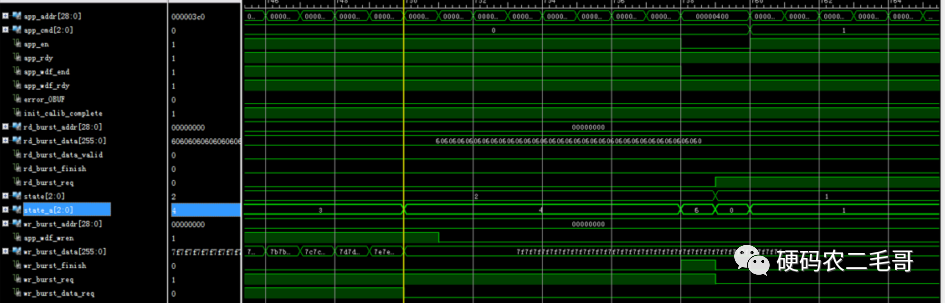

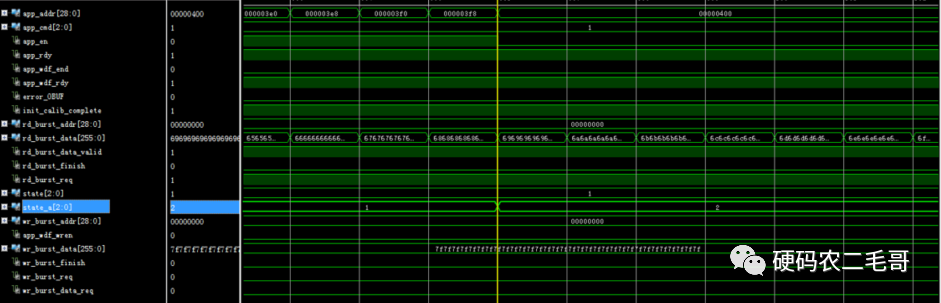

DDR写时序

数据写入DDR时,将 wr_burst_req置1,首地址写入wr_burst_addr,设置突发长度wr_burst_len 10为100,进入写状态,wr_burst_data_req为1时,将要写入数据赋值到wr_burst_data_reg,如图所示。

wr_burst_data_req下降沿之后的wr_burst_data_reg中的数据,为写入DDR最后一个数据。当wr_burst_finish等于1后,将wr_burst_req置0,完成写操作。

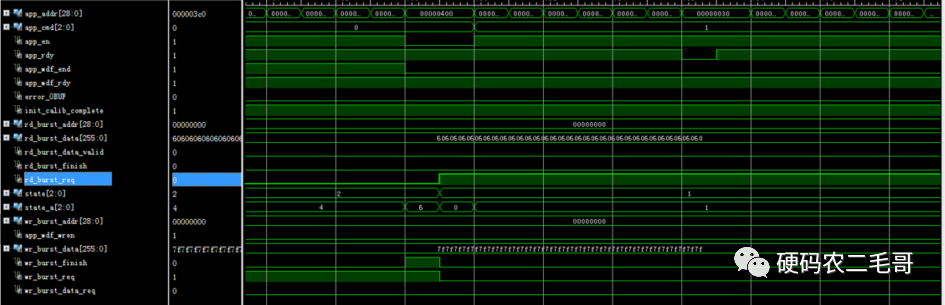

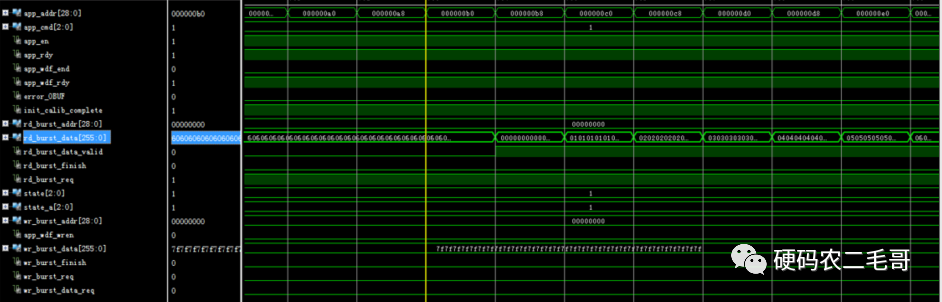

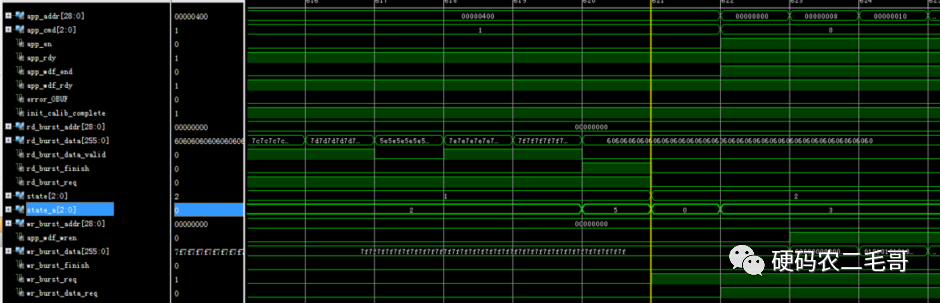

DDR读时序

从DDR读取数据时,将rd_burst_req置1,输入读首地址rd_burst_addr,设置突发长度rd_burst_len为100,进入读状态,rd_burst_data_valid为1时输出读数据。

当rd_burst_finish 等于1时,将rd_burst_req置0。完成读操作。