作者: 张大侠,文章来源: 傅里叶的猫微信公众号

上一篇文章我们讲到7系列FPGA的时钟结构,这篇文章我们来看下clock region内部都有哪些东西?

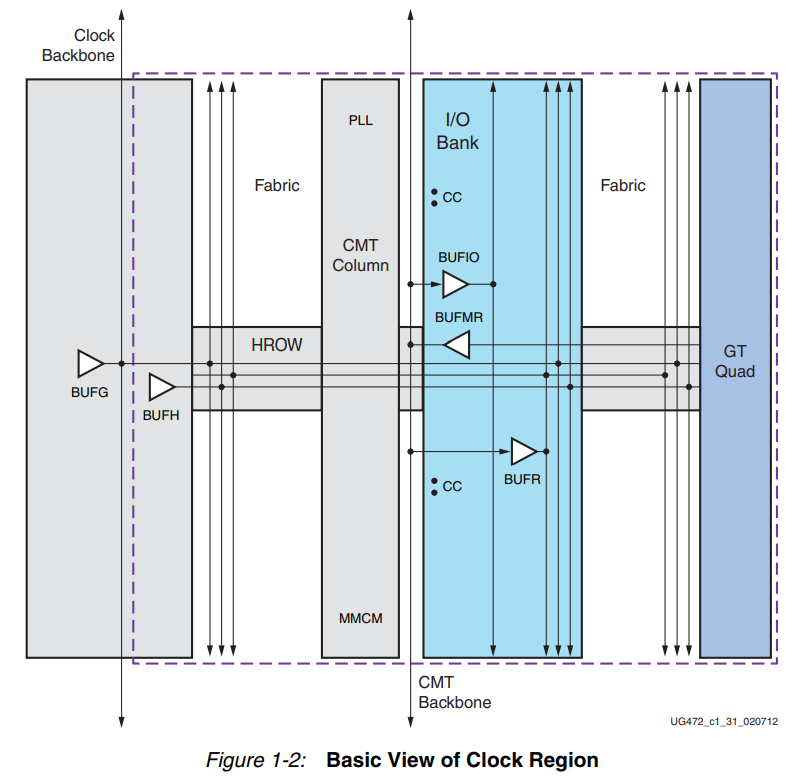

下面这个图是7系列FPGA的clock region的结构图:

首先我们来明确几个Buffer的含义(我们后面会有一篇文章专门来讲这几个buffer)

BUFG:global clock buffer

BUFH:horizontal clock buffer,可驱动左右相邻的两个region

BUFR:regional clock buffer,从名字就可以看出来,只能驱动当前region

BUFIO:I/O buffer,位于IO Bank中,只能用于驱动IO

BUFMR:multi-clock region buffer,它可以驱动本BANK和上下相邻BANK的BUFIO和BUFR,起到了扩展连接的作用

CC:clock capable

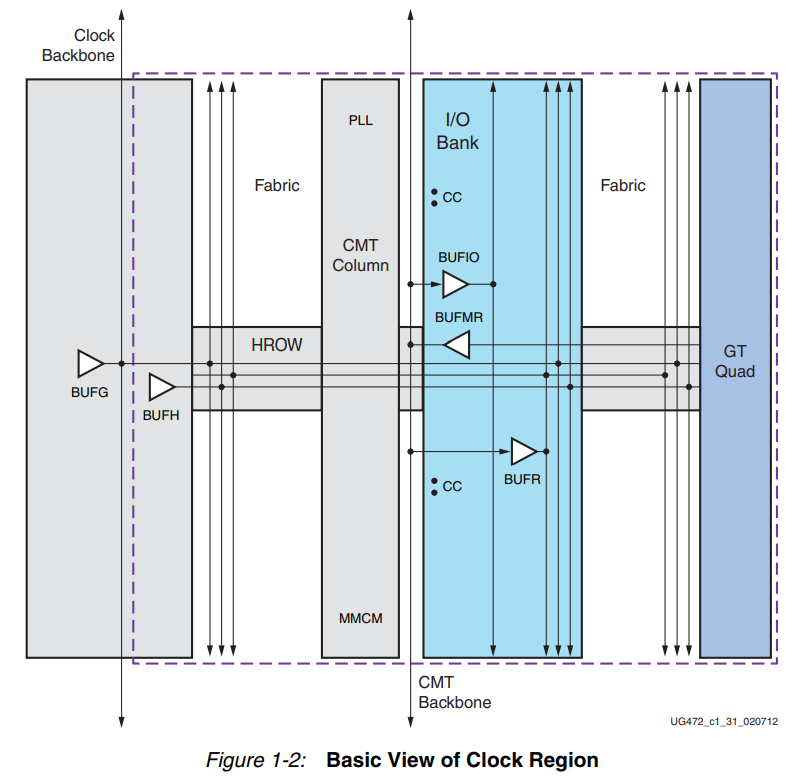

下图是clock region更详细的内部结构图,

可以看到:

每个IO Bank的4个cc管脚可以驱动CMT中的PLL/MMCM,也可以驱动BUFH;

HROW中有12个routing track,BUFG和BUFH共享12个track;

GT Quad有10个专门的track用于驱动CMT和clock backbone中的BUFFER;

BUFR有4个track驱动逻辑资源、CMT和BUFG;

CMT在一定条件下可以通过CMT backbone驱动上下相邻的CMT;

一个region中的时钟资源可以驱动本region或者水平临近region的时钟BUFFER;

CMT、cc管脚和GT时钟可以通过BUFH来驱动左右相邻region

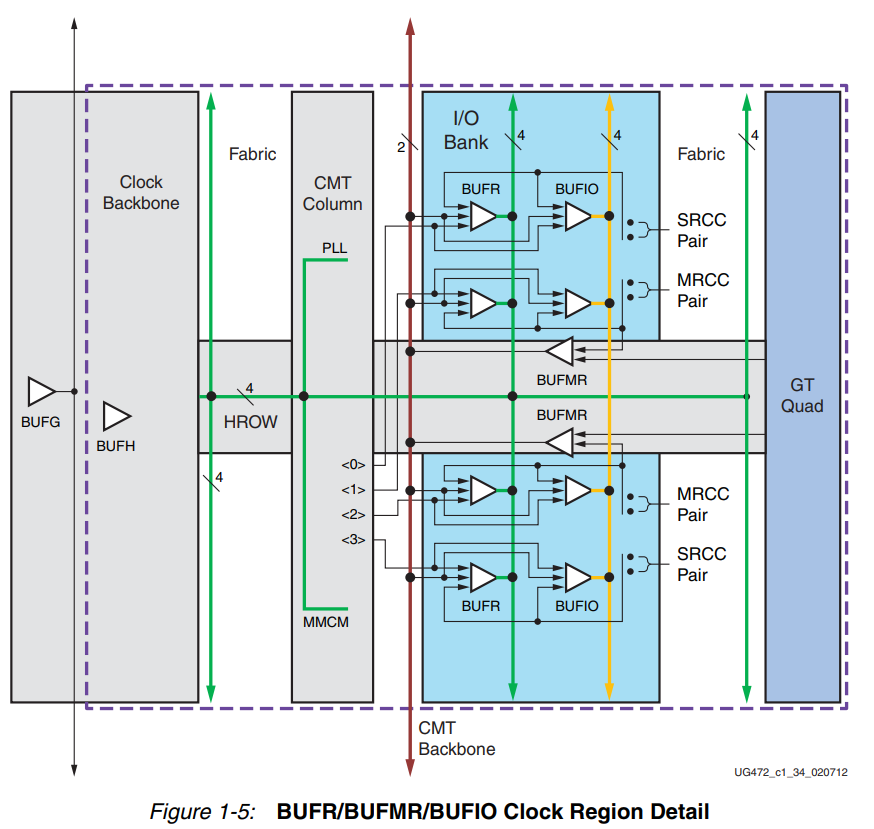

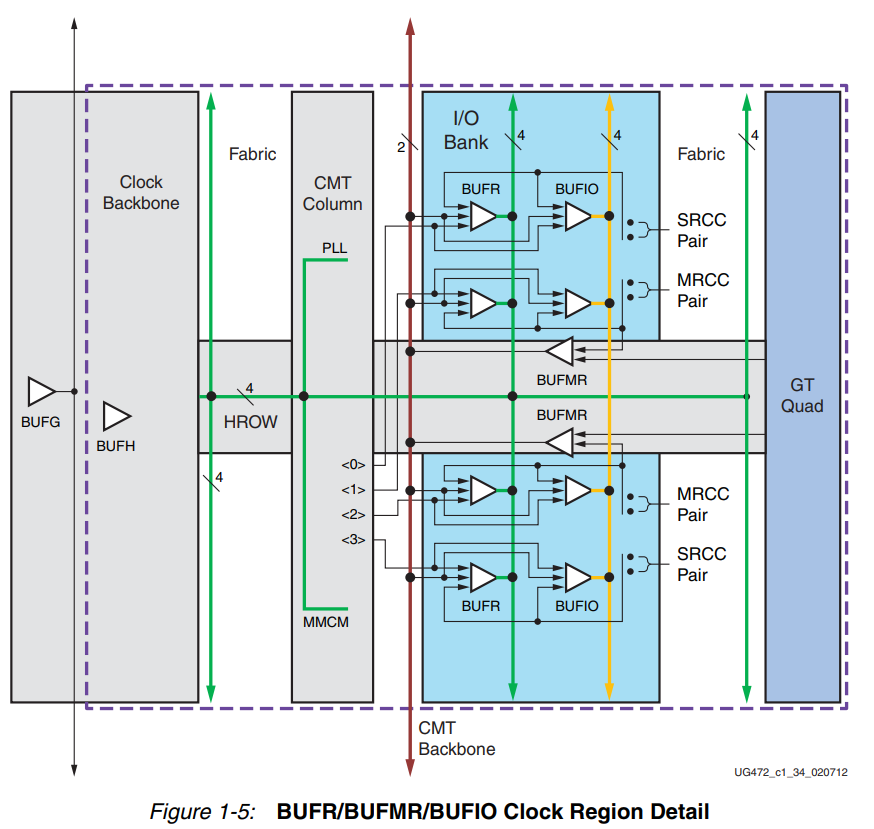

下图是BUFR/BUFMR/BUFIO的详细结构图,

可以看出:

每个IO Bank都含有4个BUFIO和BUFR;

clock buffer都可以被cc管脚或者MMCM来驱动;

图中可以看到CC又分了MRCC和SRCC,它们的区别我们放到下一篇文章中专门来讲;

从MMCM输出到BUFR和BUFIO之间有一条专门的高性能差分路径;

这里需要说明的一点是,不是所有的7系列FPGA的时钟结构都像上面的图中所画,比如包含不同数量的GT可能会导致时钟结构位置不太一样,但这并不妨碍上面这些图对7系列FPGA时钟结构的说明。