本文转载自:FPGA技术实战

注:本文由作者授权转发,如需转载请联系作者本人

引言:本文介绍Xilinx FPGA外接DDR3时钟相关参数及配置。

1.DDR3芯片时钟、位宽和数据带宽

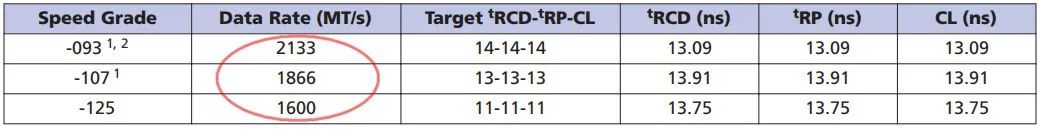

以MT41K256M16RH-125为例,DDR3关键时序参数如图1所示。

1.1 DDR3芯片 I/O接口时钟

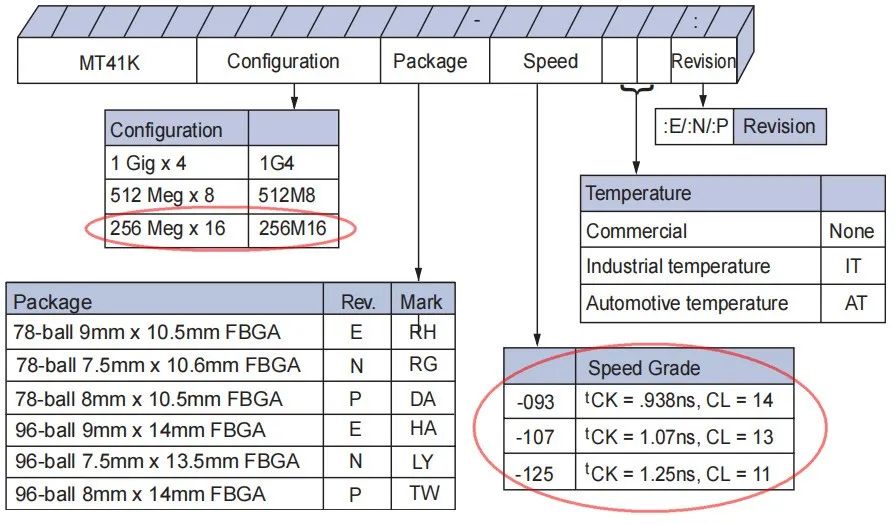

DDR3器件尾缀-1.25表示器件工作时钟周期为1.25ns,DDR3最大时钟CK/CK#=1/1.25ns=800MHz。

图1、DDR3关键时序参数

1.2 DDR3芯片位宽

图2中所示,芯片MT41K256M16RH-125配置为256M×16表示DDR3芯片位宽16bit。如若FPGA外挂2片该DDR3芯片,则位宽扩展为2*16bbit=32bit。

图2、DDR3芯片型号释义

1.3 DDR3芯片数据带宽

图1中,以DDR3 I/O最大时钟CK/CK#=800MHz计算,DDR3在时钟双沿传输数据,因此,数据速率=2*800M*16bit/s=1600MT*16=25600Mbit/s=3.125GB/s。

2.FPGA I/O支持DDR3速率

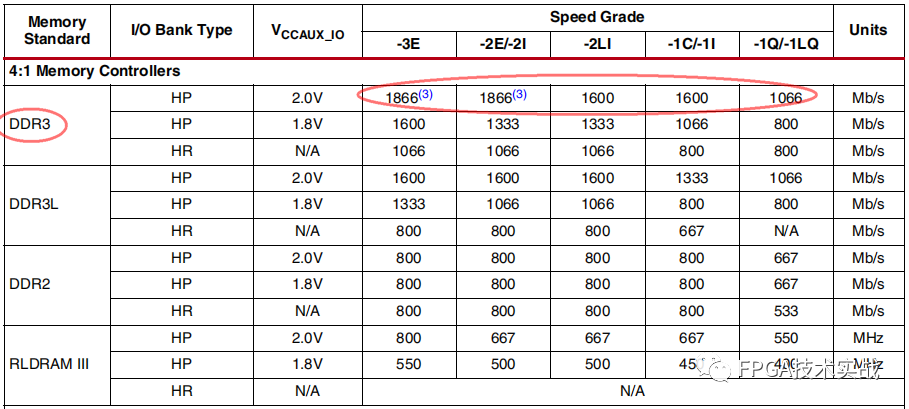

根据ZYNQ-7000器件手册,表1给出了ZYNQ-7000支持的DDR3速率。

表1、FPGA I/O支持DDR3外设最大接口数据速率

表1中,DDR3 IP运行最大1866Mb/s速率时,Vccaux_io供电电压需要提供2.0V电压,且需要连接至HP类型bank。

3.FPGA DDR3 IP核时钟

3.1 FPGA DDR3 MIG IP核时钟架构

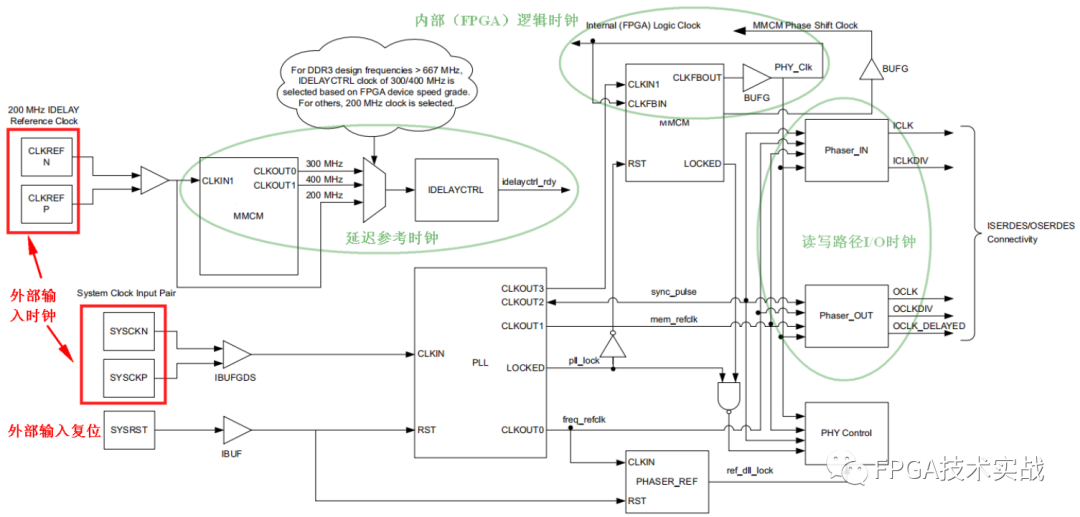

图3、DDR3 MIG IP核时钟架构

图3中所示,CLKREFP/CLKREFN为IP核参考时钟,用于配置IP核延迟MMCM模块;SYSCLKP/SYSCLKN为IP核输入时钟,用于PLL产生读写路径各个工作时钟。

3.2 FPGA DDR3 MIG IP核时钟配置

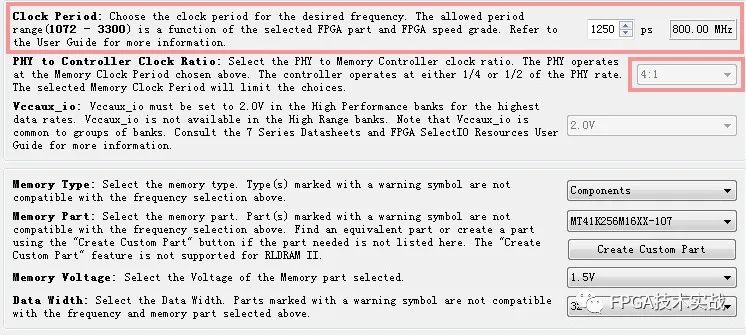

3.2.1 Clock Period时钟

Clock Period时钟参数为DDR3 I/O接口CK/CK#时钟,该时钟不能超过DDR3芯片和FPGA支持DDR3最大时钟。

图4、Clock Period时钟

3.2.2 ui_clk时钟

ui_clk时钟为DDR3 IP核应用接口用户时钟,用于实现用户接口控制及数据同步时钟。如图4所示,PHY to Controller Clock Ratio比例为4:1,则ui_clk=Clock Period/4 = 800MHz/4=200MHz。

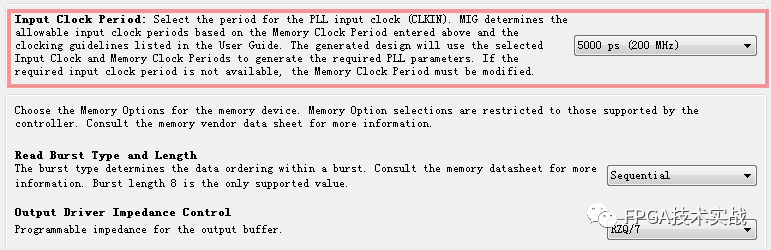

3.2.3 Input Clock Period时钟

图5、Input Clock Period时钟

该时钟为图3中DDR3 IP核SYSCLKP/SYSCLKN时钟。

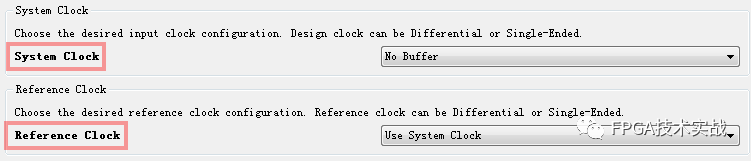

3.2.4 Reference Clock时钟

图6中System Clock时钟即图5中所配置时钟;图6中Reference Clock时钟为延迟参考时钟输入时钟,可以选择单独输入或者System Clock。

图6、System Clock&Reference Clock时钟