本文转载自: FPGA打工人微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

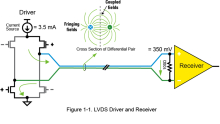

LVDS是一种低摆幅的差分信号技术,使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

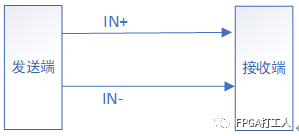

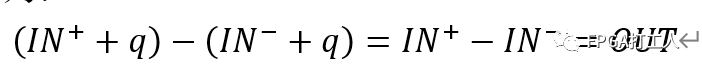

从差分信号传输线路上可以看出,若是理想状况,线路没有干扰时,可以形象理解为:

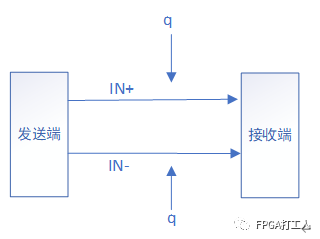

在实际线路传输中,线路存在干扰,并且会同时出现在差分线对上:

但是最后接收结果为:

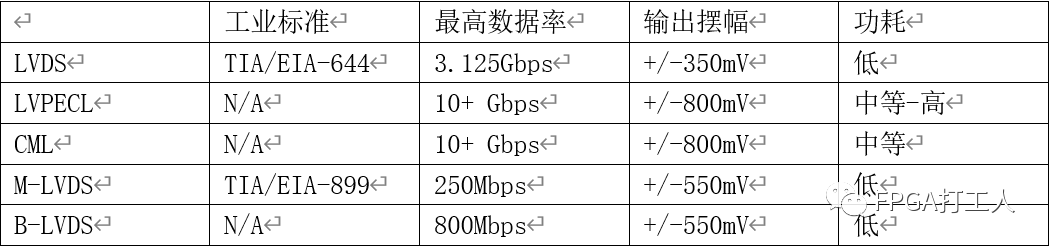

各种LVDS技术的工业标准如下:

常用的LVDS信号要求传输线阻抗受控,其中单线阻抗为50欧,差分阻抗为100欧。

UltraScale 器件中的差分信号接口

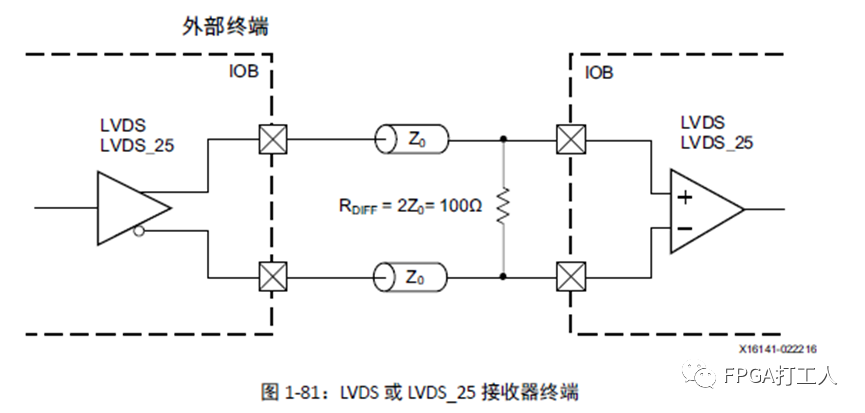

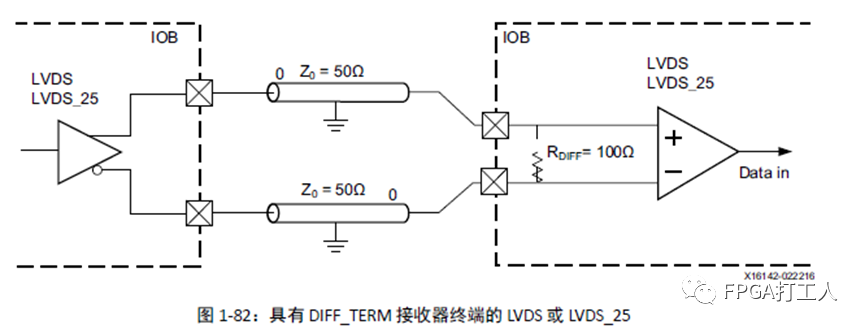

常用的有LVDS和LVDS_25这2种差分信号接口,LVDS标准仅在HPI/O bank中可用,要求输出和输入的Vcco供电电压为1.8V;HR I/O bank中提供了LVDS_25标准,要求输出和输入的Vcco供电电压为2.5V。

作为接收时,匹配电阻在FPGA内部是可选项,具体由DIFF_TERM_ADV或DIFF_TERM,若外部开发板没有匹配电阻,需要设置DIFF_TERM_ADV =TERM_100或者DIFF_TERM = TRUE。

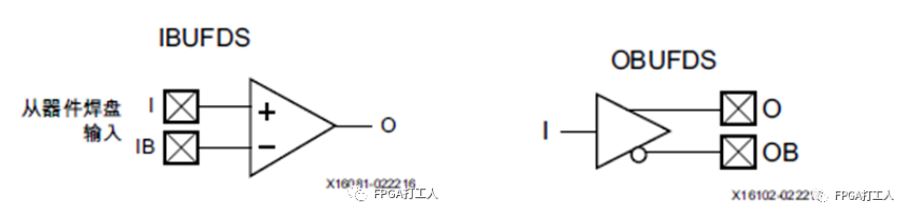

最主要的两个原语是IBUFDS和OBUFDS。IBUFDS对应的是接收,OBUFDS对应的是发送。

下面是LVDS I/O标准的允许属性