本文转载自:FPGA技术实战的CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

引言:

7系列FPGA支持非常宽的I/O电压标准,本文介绍以下典型的I/O电压标准及端接匹配电路:

LVTTL I/O标准

LVCMOS I/O标准

TMDS I/O标准

LVDS和LVDS_25 I/O标准

1 .LVTTL(低压TTL)

LVTTL支持的I/O bank类型如图1所示。

内容

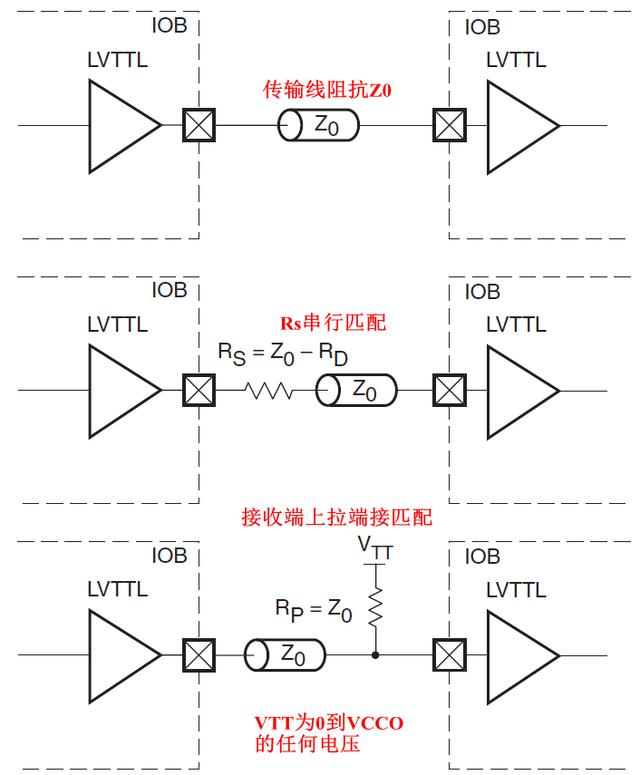

LVTTL是一般用于3.3V外设接口中,它使用单端COMS输入缓冲器和推挽输出缓冲器。该标准要求3.3V输出源电压(Vcco),但是不要求参考电压(VREF)或者端接电压(VTT)。图2显示了单向LVTTL端接技术。

图2、LVTTL单向端接方式

在图2所示中,最上面图没有采用端接,直接将输出驱动器连接至接收器,当信号为高速信号时,我们通常将该PCB走线阻抗控制为50欧姆;中间图采用了串行匹配,即在PCB走线上串入电阻Rs,该电阻可以减少信号长距离传输的振铃效应。最下面在接收器侧采用并行端接方式,在传输线末端减少信号反射以保持信号传输的完整性。对于LVTTL电平常见上面两种情况。

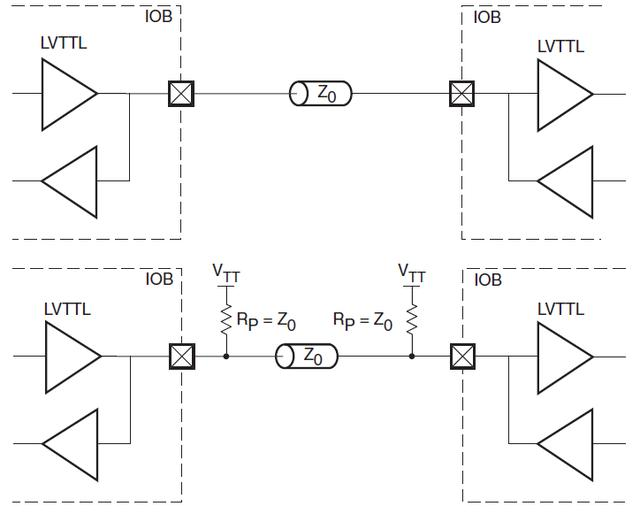

图3显示了双向LVTTL I/O端接方式。

图3、LVTTL双向端接方式

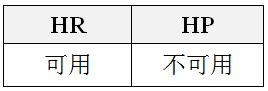

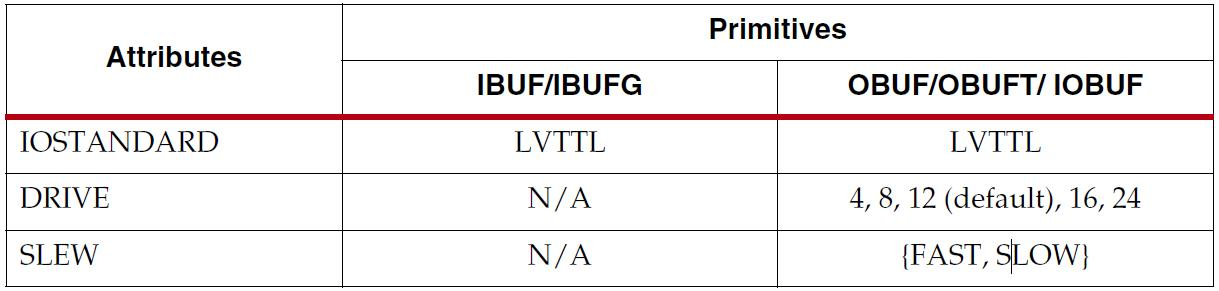

LVTTL可编程属性如图4所示,该标准只能在HR I/O banks中可用。

图4、LVTTL I/O标准可用属性

2 .LVCOMS(低压CMOS)

LVCMOS可用的I/O bank类型如图5所示。

图5、LVCMOS I/O可用的bank类型

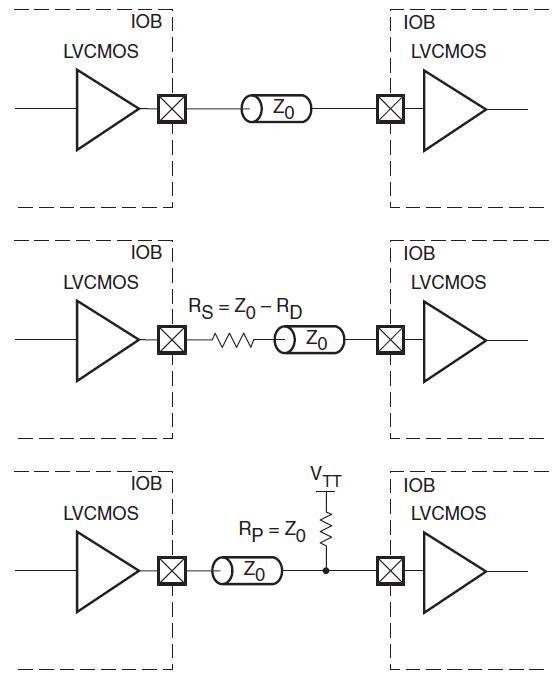

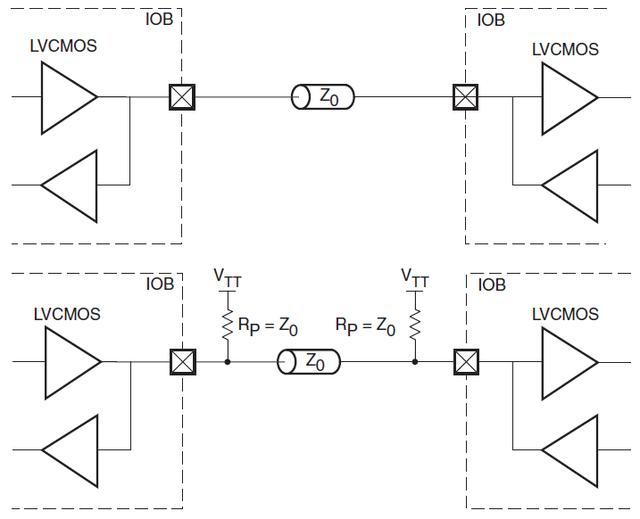

7系列FPGA支持的LVCMOS标准:LVCMOS12、LVCOMS15、LVCMOS18、LVCMOS25和LVCMOS33。这几种LVCMOS I/O标准支持的输出驱动电流存在差异。单向和双向LVCOMS端接方式和LVTTL类似。图6和图7分别举例单向和双向LVCOMS端接方式。

图6、LVCMOS单向端接方式

图7、LVCMOS双向端接方式

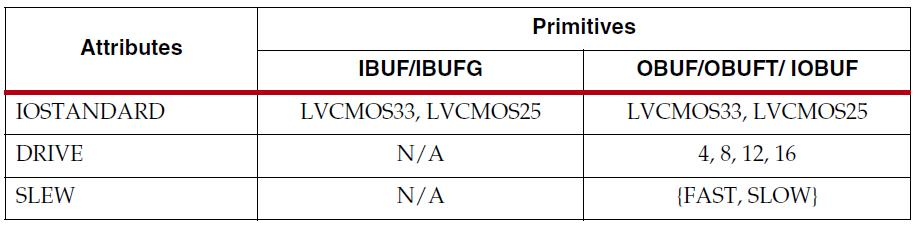

LVCMOS25和LVCMOS33 I/O标准只能在HR I/O bank中应用,它们的编程属性如图8所示。

图8、LVCMOS25和LVCMOS33 I/O编程属性

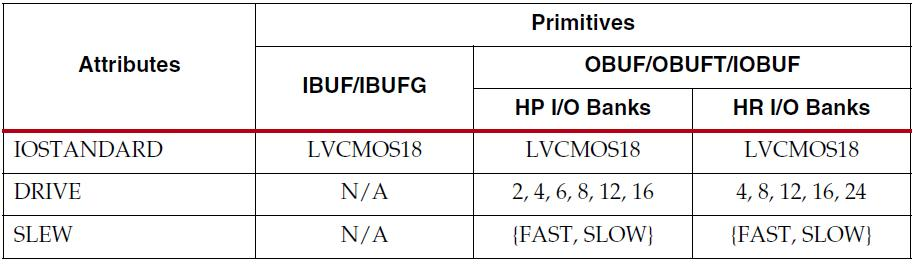

LVCMOS18 I/O标准在HR和HP bank中都可以应用,它们的编程属性如图9所示。

图9、LVCMOS18 I/O标准编程属性

LVCMOS15 I/O标准在HR和HP bank中都可以应用,它们的编程属性如图10所示。

图10、LVCMOS15 I/O标准编程属性

LVCMOS12 I/O标准在HR和HP bank中都可以应用,它们的编程属性如图11所示。

图11、LVCMOS12 I/O标准编程属性

3 .TMDS

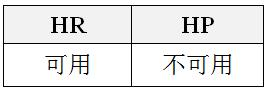

TMDS支持的I/O bank类型如图12所示。

图12、LVTTL可用的I/O bank类型

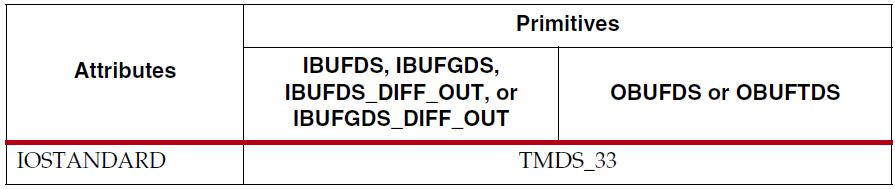

TMDS是一种差分I/O标准,用于DVI和HMDI视频接口,实现高速串行数据流传输。TMDS标准要求输入外部50Ω上拉电阻至3.3V,不要求差分输入端接电阻。该标准只能在HR I/O bank中应用,并且要求bank Vcco电压为3.3V。TMDS I/O编程属性如图13所示。

图13、TMDS I/O编程属性

4 .LVDS和LVDS_25

LVDS作为一种高速接口在很多应用中使用,7系列FPGA I/O LVDS接口兼容EIA/TIA电气特性要求。IOB内部支持可选的内部差分端接,在点对点应用中,可以消除外出源端接电阻,简化PCB设计。

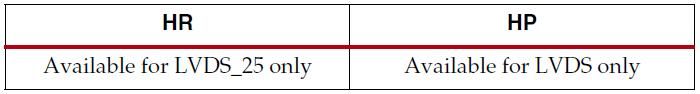

LVDS I/O标准只在HP I/O bank中可用。LVDS输出和输入要求Vcco供电为1.8V,内部可选端接属性DIFF_TERM。LVDS_25 I/O标准只在HR I/O bank中可用。LVDS_25输出和输入要求Vcco供电为2.5V,内部可选端接属性DIFF_TERM。可用I/O bank类型如图14所示。

图14、可用的I/O bank类型

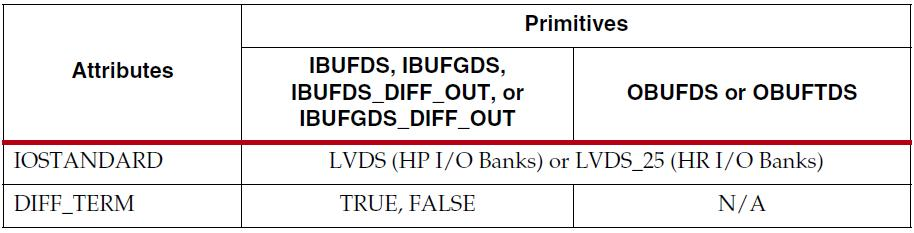

发送端接:7系列FPG发送端不需要外部端接。图15给出了LVDS电流驱动器允许的编程属性。

图15、LVDS电流驱动器允许的编程属性

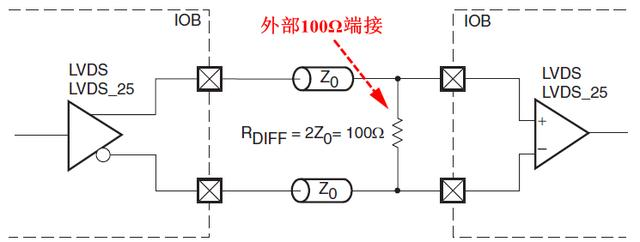

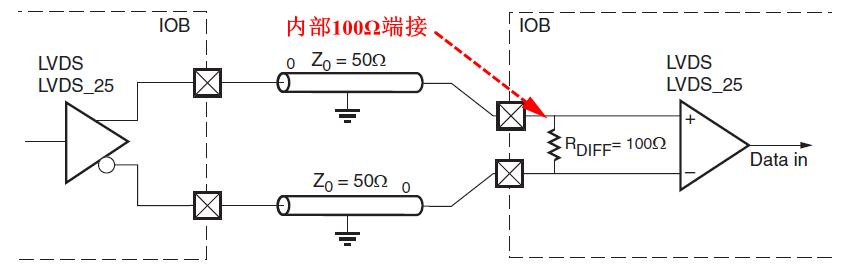

接收端:图16和图17显示了LVDS和LVDS_25接收器差分端接举例。

图16、LVDS或LVDS_25接收器外部端接

图17、LVDS或LVDS_25接收器内部端接

在I/O bank中允许有LVDS和LVDS_25两种电平输入,而输出必须满足要求的电压(LVDS要求1.8V输出电压,LVDS_25要求2.5V输出电压),不能同时输出两种电平,以下规则必须满足:

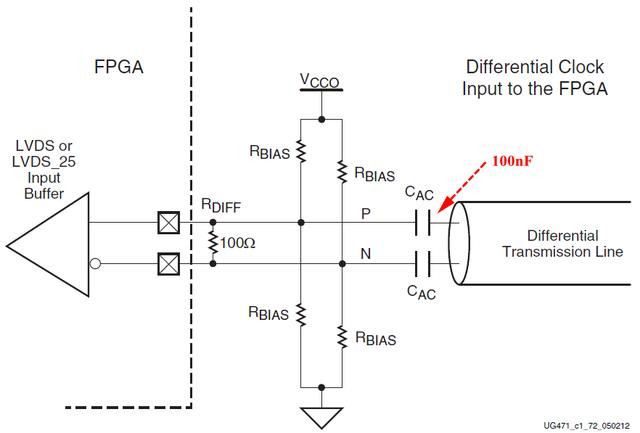

图18给出了满足以上要求的端接方式。图中使用外部端接100Ω,四个偏置电阻阻值必须一样,且阻值范围为10k~100k,AC耦合电容为100nF。所有的阻容器件必须靠近FPGA输入管脚。

图18、差分时钟输入AC耦合和DC偏置电路