本文转载自:孤独的单刀的CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

之前笔者也是被7系列的一大堆BUFG、BUFH、BUGR等等BUF搞得头都晕了,加上平时一般只用BUFG这个全局时钟缓冲,导致一直对7系列的时钟资源理解不多。下面就一起把官方手册《UG472:7 Series FPGAs Clocking Resources》的第一章节(时钟结构部分)好好研究研究。

正文部分的黑色字翻译自UG472,蓝色字为笔者理解。

一、时钟结构概述

7系列FPGA的时钟资源通过专用的全局和区域I/O和时钟资源管理复杂和简单的时钟需求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,则在设计时钟功能时不推荐使用。

全局时钟树允许同步元素的时钟跨越设备

I/O时钟和区域时钟树允许最多三个垂直相邻的时钟区域的时钟

每个时钟管理块(CMT)包含一个混合模式时钟管理器(MMCM)和一个锁相环(PLL),位于I/O列旁边的CMT列

为了时钟使用,每个7系列设备被划分为多个时钟区域。

时钟区域的数量随着设备大小的不同而变化,最小的设备上有一个时钟区域,最大的设备上有24个时钟区域。

一个时钟区域包括所有同步元素(例如:CLB、I/O、串行收发器、DSP、块RAM、CMT),该区域跨越50个CLB和一个I/O BANK(50个I/O),其中心有一个水平时钟行(HROW)。

每个时钟区域从HROW向上跨越25个CLB,从HROW向下跨越25个CLB,并且水平地跨越设备的每一侧

二、时钟布线资源概述

每个I/O BANK包含有支持时钟(clock-capable)的输入引脚,用于将用户时钟带到7系列FPGA时钟布线资源。与专用时钟缓冲器相比,支持时钟的输入将用户时钟送到:

全局时钟线在同一设备的上/下半部

I/O时钟线在相同的I/O BANK和垂直相邻的I/O BANK内

在相同的时钟区域内的区域时钟线和垂直相邻的时钟区域

CMT,在有限情况下的同一时钟区域,和垂直相邻的时钟区域

每个7系列单片设备有32个全局时钟线,可以提供时钟和控制信号到整个设备中的所有时序资源。全局时钟缓冲器(BUFGCTRL,在本用户指南中被简化为BUFG)驱动全局时钟线,而且必须用于访问全局时钟线。使用时钟区域中的12个水平时钟线则可以做到每个时钟区域最多可以支持12个这样的全局时钟线。

全局时钟缓冲:

可以用作时钟使能电路来使能或禁用跨越多个时钟区域的时钟

可以作为无故障的多路复用器:

选择两个时钟源

更换故障的时钟源

经常被CMT驱动来用于:

消除时钟分布延迟

调整相对于另一个时钟的时钟延迟

水平时钟缓冲器(BUFH/BUFHCE)允许通过水平时钟行访问单个时钟区域中的全局时钟线。它也可以用作时钟使能电路(BUFHCE)来独立地使能或禁用跨越单个时钟区域的时钟。使用每个时钟区域中的12条水平时钟线则可以做到每个时钟区域最多可以支持12个时钟。

每个7系列FPGA都有区域和I/O 时钟树,它们可以为一个时钟区域内的所有时序资源提供时钟。每个设备还具有多时钟区域缓冲器(BUFMR),BUFMR允许区域时钟和I/O 时钟跨越三个垂直相邻的时钟区域。

I/O时钟缓冲器(BUFIO)驱动I/O时钟树,提供对同一I/O库中所有时序I/O资源的时钟访问。

区域时钟缓冲器(BUFR)驱动区域时钟树,该时钟树驱动同一时钟区域内的所有时钟目的地,可以通过编程来划分传入的时钟速率。

结合IOB中的可编程序列化器/反序列化器(参见UG471, 7系列fpga的SelectIO资源用户指南中的Advanced SelectIO逻辑资源章节),BUFIO和BUFR时钟缓冲区允许源同步系统在不使用额外逻辑资源的情况下跨时钟域。

当与相关的BUFR和BUFIO一起使用时,可以使用多时钟区域缓冲区(BUFMR)驱动相邻时钟区域的区域时钟、I/O时钟树和I/O BANK

最多支持四个独特的I/O时钟和四个独特的区域时钟。

高性能时钟路由将时钟管理块(CMT)的特定输出以非常低的抖动、最小的占空比失真直接连接到I/O上。

三、时钟管理块概述

每个7系列FPGA有多达24个CMT,每个CMT由一个MMCM和一个PLL组成。MMCM和PLL可作为广泛频率范围的频率合成器,可作为外部或内部时钟抖动滤波器以及低偏移时钟。PLL可以看作是MMCM的一个功能子集。7系列FPGA时钟输入连接允许多个资源为MMCM和PLL的参考时钟。

7系列fpga的MMCM在任意方向都具有无限的精细相移能力,可用于动态相移模式。MMCM在反馈路径和输出路径中有一个分数计数器,这使得频率合成能力的精度进一步提高。

LogiCORE™ IP时钟向导可用于帮助利用MMCMs和PLL在7系列FPGA设计中创建时钟网络。图形用户界面用于采集时钟网络参数。计时向导选择适当的CMT资源,并以最佳方式配置CMT资源和关联的时钟路由资源。

四、时钟缓冲、管理和布线

图1-1是7系列fpga时钟架构的高层次视图。垂直时钟中心线(时钟主干道the clock backbone)将设备划分为相邻的左和右区域,而水平中心线将设备划分为其顶部和底部两侧。时钟主干道中的资源被镜像到水平相邻区域的两侧,从而将某些时钟资源扩展到水平相邻区域。顶部和底部分隔分隔了两组全局时钟缓冲器(BUFG),并对它们的连接方式施加了一些限制。但是BUFG不属于一个时钟区域,可以到达设备上的任何一个时钟点。所有水平时钟资源都包含在时钟区域水平时钟行(HROW)的中心,垂直的、非区域的时钟资源则包含在时钟主干道或CMT主干道中。

一个时钟区域总是每列包含50个clb、10个36K块RAM(除非5个36K块被PCIE的集成块替代),每列包含20个DSP Slice和12个BUFH。一个时钟区域包含,一个CMT (PLL/ MMCM),一个50个IO BANK,一个由四个串行收发器组成的GT Quad,以及在块RAM列中为PCIe的半列。

图1-1是7系列时钟资源的大致结构。时钟主要由三个部分组成:全局时钟、局部时钟和I/O时钟。

BUFG即为全局时钟缓冲,Backbone是时钟布线的主干道,BUFG通过它可以到达任意一个时钟区域,而且BUFG通过HROW到达时钟区域内部的每个逻辑单元。

BUFH即为水平时钟缓冲器,它相当于一个功能受限的BUFG,其输出时钟只能通过HROW在左右相邻的时钟区域内工作。

BUFIO即为IO时钟缓冲,其输出时钟只能作用在一个时钟区域的IO寄存器处,无法在FPGA内部逻辑使用。

BUFR即为区域时钟缓冲,其输出只能作用在一个时钟区域。

BUFMR即为多区域时钟缓冲器,其输出作用在本时钟区域,还可以通过CMT Backbone作用在上下相邻两个时钟区域。

MMCM、PLL即时钟管理模块,用来消除时钟的延迟、抖动以及产生各种不同频率的时钟。

CC即为外部时钟输入管脚,其管脚在内部可以连接到BUFG、BUFR、BUFIO、BUFH、MMCM、PLL等,看具体的应用具体连接。一个时钟区域有4对CC管脚,其中2对SRCC,2对MRCC。SRCC作为区域时钟使用时,只能连接本时钟区域的BUFR和BUFIO。而MRCC则还可以通过BUFMR作用在上下相邻的时钟区域。

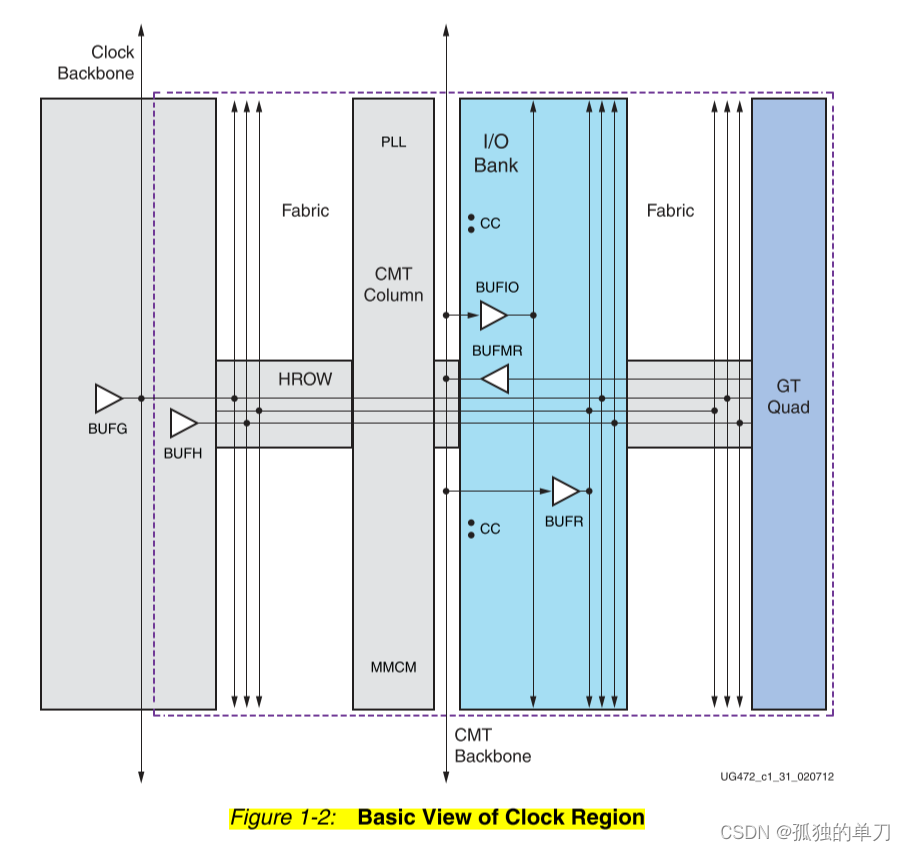

图1-2是一个时钟区域内可用时钟资源的高层次概览,以及它们的基本连接。全局时钟缓冲器可以通过HROW驱动到每个区域,即使再物理空间上不位于那里。水平时钟缓冲器(BUFH)通过HROW驱动到区域中的每个时钟点。BUFG和BUFH在HROW中共享路由通道。I/O缓冲区(BUFIO)和区域时钟缓冲区(BUFR)位于I/O BANK内部。BUFIO只驱动I/O时钟资源,BUFR驱动I/O资源和逻辑资源。BUFMR支持BUFIO和BUFR的多区域链接。具有时钟能力的输入将外部时钟连接到设备上的时钟资源。某些资源可以通过CMT主干道连接到上面和下面的区域。

图1-3为设备右侧单个时钟区域的时钟详细图:

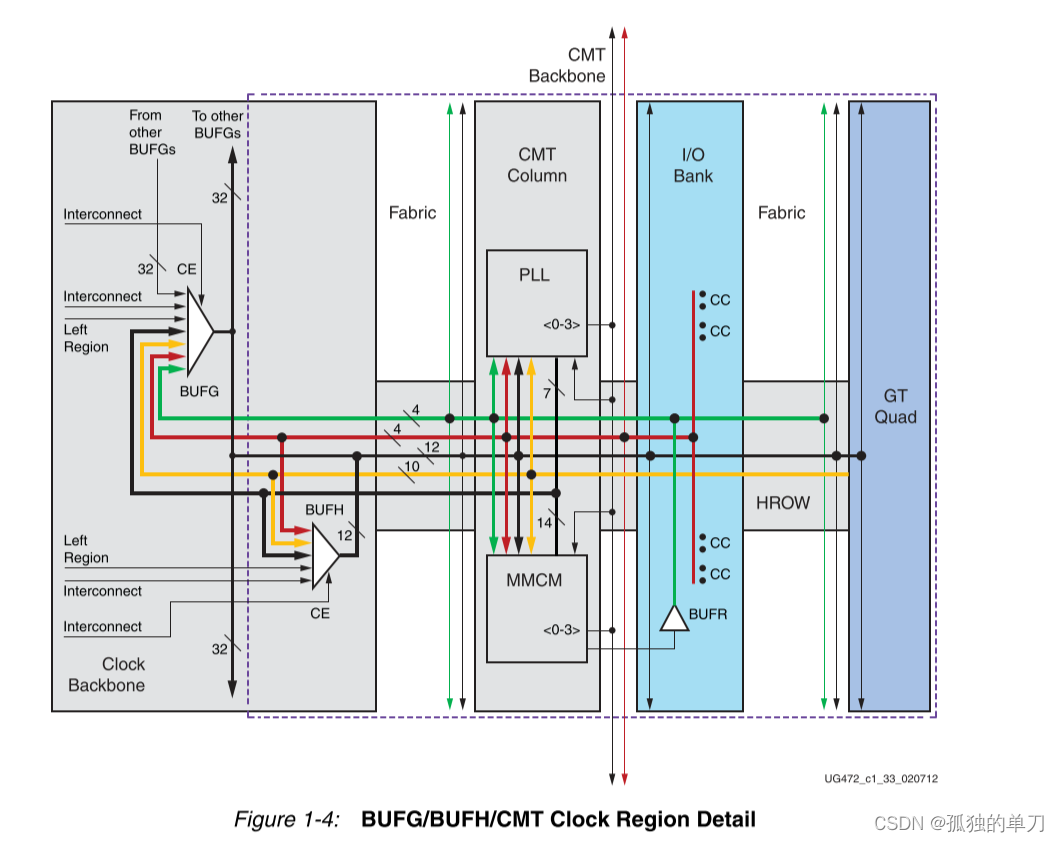

图1-4显示了全局BUFG和区域BUFH/CMT/ CC管脚连接性的详细图,以及区域中可用资源的数量(显示为右侧区域)。

4个时钟输入引脚中的任何一个都可以驱动CMT中的的PLL/MMCM和BUFH。BUFG显示在该区域中,但在物理空间上可以位于时钟主干道中的其他物理位置。BUFG和BUFH共享HROW中的12个路由轨道,可以驱动该区域内的所有时钟点。BUFG也可以驱动BUFH(图1-4中没有显示)。这允许在其他全局时钟分布上单独启用时钟(CE)。一个GT Quad有10条专用路径来驱动CMT和时钟主干道中的时钟缓冲器。位于I/O BANK的BUFR在逻辑、CMT和BUFG中有四个驱动时钟点。CMT可以使用CMT主干道驱动相邻区域的其他CMT,但有一定的局限性。类似地,具有支持时钟的引脚可以在相同的限制下驱动相邻区域的CMT。具有支持时钟的引脚可以驱动BUFG在设备相同的顶部/底部的任何位置。在CMT主干道中有四个通道支持垂直区域之间的连接。来自一个区域的时钟源可以驱动其自身区域内的时钟缓冲区资源,也可以驱动水平相邻区域内的时钟缓冲区资源。CMT、支持时钟引脚和串行收发器可以通过BUFH将时钟驱动到水平相邻区域,也可以连接到设备相同的顶部/底部的BUFG。

逻辑互连驱动BUFG和BUFH的CE引脚。逻辑互连也可以驱动时钟进入相同的缓冲器,但必须小心,因为时间是不可预测的。

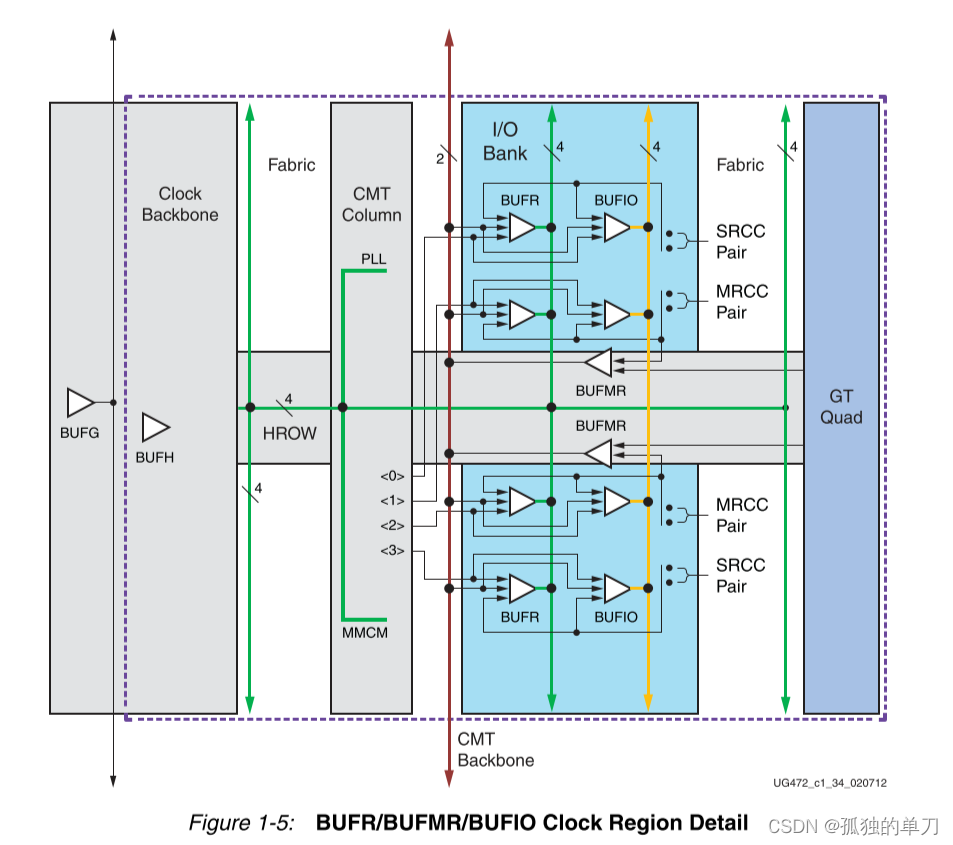

图1-5更详细地展示了I/O时钟资源和互联性。

每个I/O BANK包含4个BUFIO和4个BUFR。每个时钟缓冲器可以被一个特定的具有支持时钟管脚对的输入时钟驱动,也可以由MMCM的特定输出时钟直接驱动。两个支持时钟的输入管脚对,被称为MRCC,支持多区域时钟方案。一个MRCC管脚对可以驱动特定的BUFMR,而BUFMR又可以驱动相同和相邻区域中的BUFIO和BUFR,从而促进多区域/BANK接口。同样,GT Quad也可以驱动BUFMR。MMCM<3:0>的输出到BUFR和BUFIO有专用的高性能差分路径。这个特性也被称为高性能时钟(HPC)。

尽管所有7系列设备具有相同的基本架构,但在不同的系列和系列内的设备之间存在一些架构差异。每个7系列FPGA在设备的左侧边缘至少有一个完整的I/O列。GT可以是7系列fpga 支持的任意一个串行收发器(GTP、GTX或GTH)。带有GT的设备在设备的右边缘有一个GT和I/O的混合列(某些Artix-7和Kintex-7设备),或者设备的右边缘有一个完整的GT列(某些Virtex-7和Kintex-7设备)。其他Virtex-7器件的左右边缘都有完整的GT列,左右两侧都有完整的I/O列侧面。Artix-7200t器件在时钟列的顶部和底部有GTP收发器。

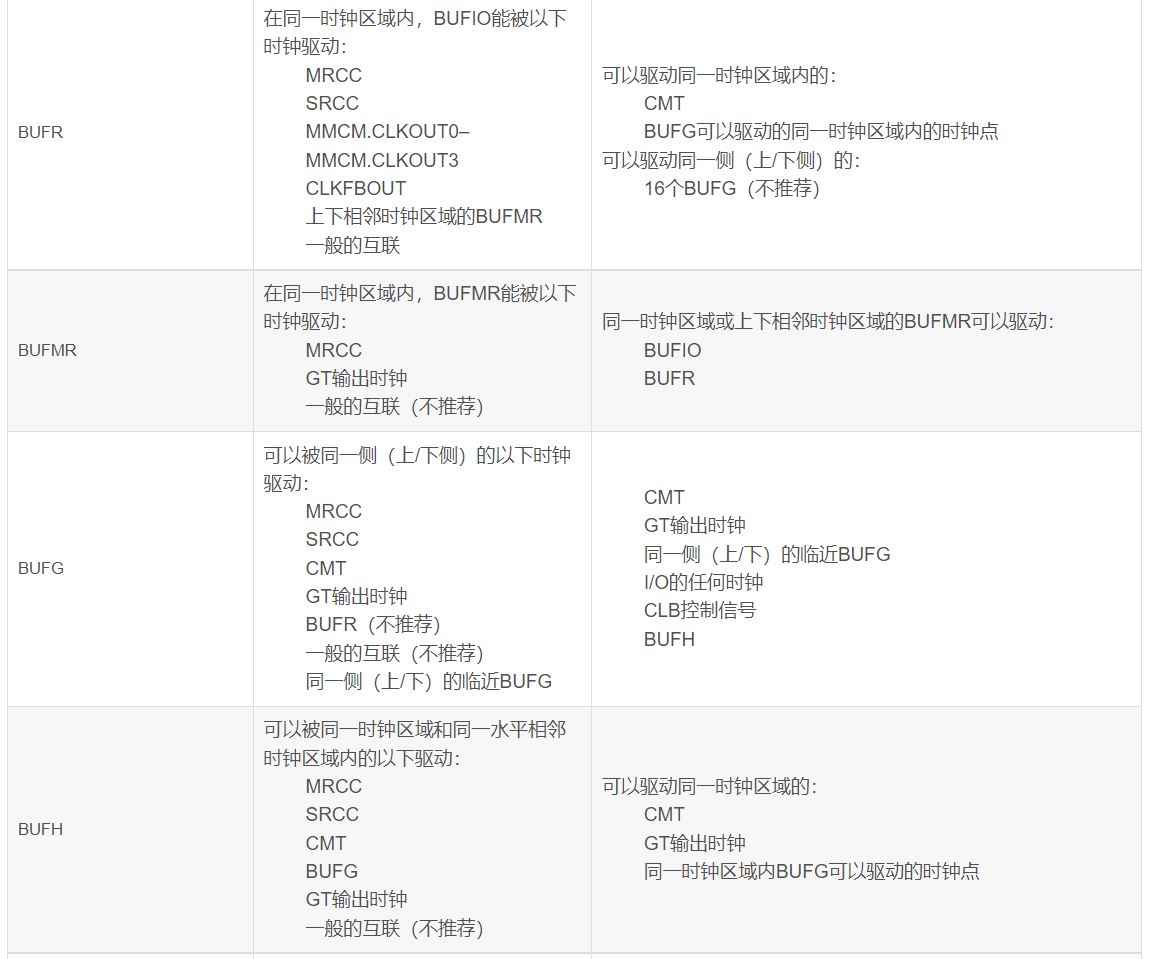

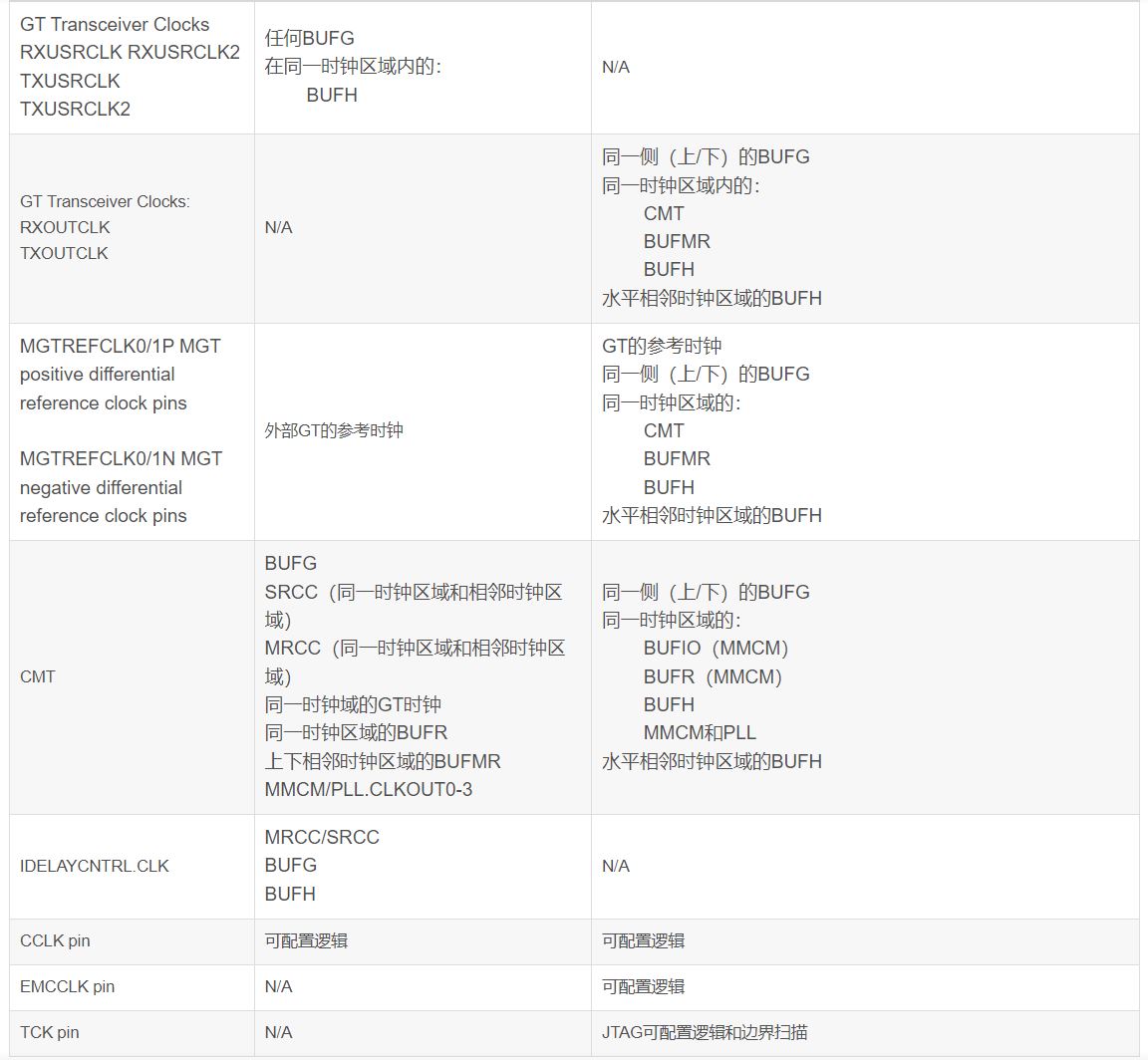

五、时钟连接概述

下表总结了7系列fpga的时钟连接。

六、总结

FPGA由多个BANK组成,每个BANK即为一个独立时钟区域

每个BANK都有一对MRCC管脚以及一对SRCC管脚来接入外部时钟(晶振等);MRCC功能大体和SRCC一样,多了一个驱动BUFMR的功能

BUFG是全局时钟,可以通过clock backbone这一时钟主干道到达每一个时钟区域;到达每个时钟区域后,可以通过HROW这一水平的主干道到达每一个点

BUFH无法到达上下的时钟区域,只能通过HROW到达水平方向内的所有BANK的点

BUFR可以驱动所在时钟区域内的所有时钟;BUFMR不光可以驱动所在时钟区域内的所有时钟,同时还可以驱动上下相邻两个时钟区域内的时钟

BUFIO是I/O区域内的时钟缓冲,只能驱动I/O资源,无法驱动内部逻辑

一个不太恰当的比喻:7系列的时钟资源就像城市内的车辆,而时钟布线资源就像是城市内的干道。有些车比较牛(BUFG),可以通过主干道(时钟主干道)到达每一个区域(时钟区域),然后通过个别几个区域内的次干道(HROW)到达每一个地点;有一些车没那么牛(BUFH),只能通过个别几个区域内的次干道(HROW)到达每一个地点;有些车就更差了(BUFR),只能在自己的小区内开开。