本文转载自: FPGA打工人微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

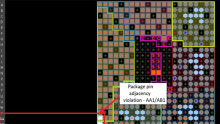

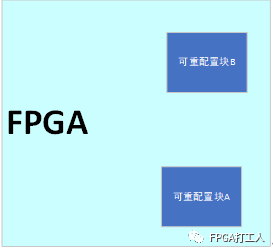

DFX功能实际上就是部分可重配置功能,开启可重配置功能时,FPGA内部的逻辑可以分割为两种不同类型:可重配置逻辑和静态逻辑,静态逻辑的功能不会由于加载可重配置逻辑的bit而受到影响。如下图所示,通过将不同的bit下载至可重配置块B或A中,就可以实现对应块的不同功能。

可重配置的支持

(1)对于7系列的器件:

1.可重配置资源包括CLB、BRAM、DSP以及布线资源,不支持时钟的可重配置,包括BUFG、MMCM、PLL等必须驻留在静态区域;

2.I/O和I/O相关的元件(ISERDES,OSERDES,IDEAYCTRL等)、串行收发器(MGT)和相关元件、集成的特性元件(BDCAN,ICAP,XDAC等)必须驻留在静态区域;

(2)对于UltraScale和UltraScale+器件:

7系列提到的除集成的特性元件(BDCAN,ICAP,XDAC等)外,其他都支持可重配置。

可重配置的流程

(1) 单独综合静态模块和可重构配置的模块;

(2) 创建物理约束(Pblock)来定义重构区域;

(3) 针对每个RP设置HD.RECONFIGURABLE属性;

(4) 实现一个完整的设计(静态设计和每个RP有一个RM);

(5) 保存用于充分布线设计的一个DCP;

(6) 从设计中去除RM,只保存静态DCP;

(7) 锁定静态布局和布线;

(8) 将新RM添加到静态设计,实现新的配置,为完整布线后的设计保存DCP;

(9) 重复第8步,直到实现所有的可重配置模块;

(10) 对所有的配置运行验证工具(pr_verify);

(11) 为每个配置创建bit;

具体实验example可参考:https://zhuanlan.zhihu.com/p/147651921

不难看出,这个流程实际上是有弊端的。此流程只适用于知道可重配置区域有几种选择,并且整个流程一次性把所有选择的bit都会生成,然后通过更改可重配置区域的bit来验证哪种选择更合适。

假如不知道该区域有几种选择,每次更改都得整个project重新跑,并且project过大,可能和之前的开发周期没太大区别。这点xilinx肯定是有考虑的,所以xilinx又推出了Abstract Shell功能,在下篇文章详细介绍。