本文转载自:FPGA技术实战的CSDN博客

Vivado CIC IP核滤波器详解(一)

引言:从本文开始,我们详细介绍Xilinx CIC IP核滤波器相关知识,包括CIC IP核提供的特性、IP核接口描述以及IP核设计指导等相关内容。

1.概述

级联积分器梳状(CIC)滤波器,也称为Hogenauer滤波器,是用于实现数字系统中大采样率变化的多速率滤波器,它们通常用于具有大的过采样率的应用中。也就是说,系统采样率远大于数字下变频器(DDC)和数字上变频器(DUC)中处理信号所占用的带宽。CIC滤波器的实现具有只使用加法器、减法器和延迟元件的结构。这些结构使得CIC滤波器对其硬件高效的多速率滤波实现很有吸引力。

2.IP核特性

Xilinx提供的CIC IP核支持以下特性:

3.IP核接口描述

图1、CIC IP核接口信号

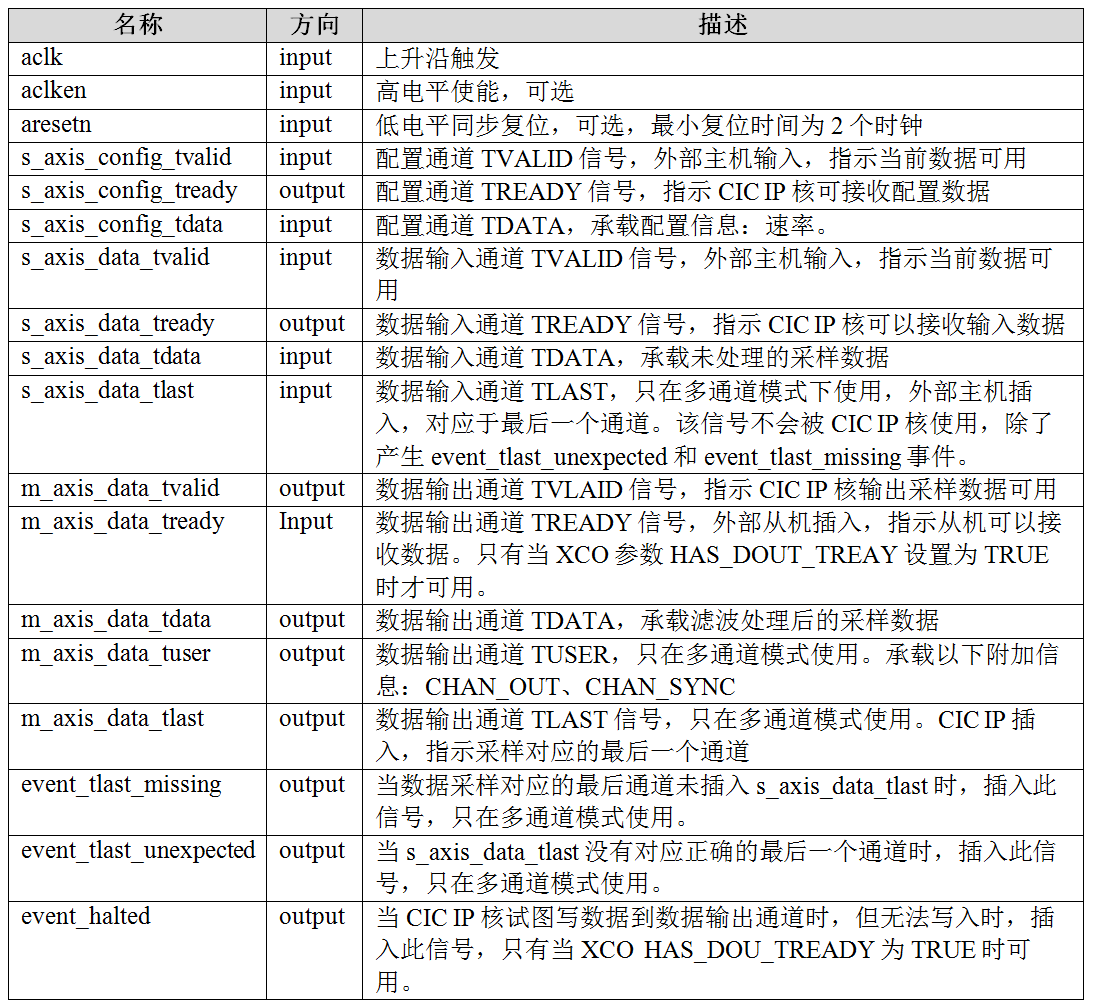

CIC IP核接口描述如表1所示。

表1、CIC IP核接口描述

4.IP核设计指导

4.1通用设计指导

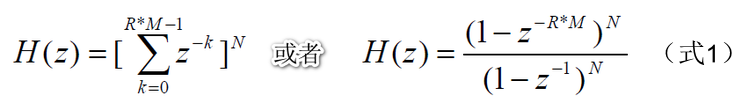

CIC滤波器的系统响应可以表示为式1:

其中,N表示CICI滤波器的级数;R表示滤波器速率改变(抽取或者内插);M表示差分延迟。

CIC滤波器的幅频相应如式2所示,式中f表示离散时间频率。

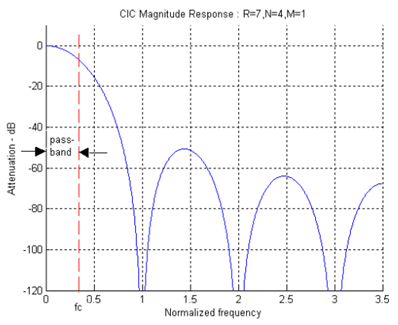

图2举例CIC幅频相应。由式2及图2,可知在f=n*(1/RM),n为整数,存在零点,因此,差分延迟M可以调整零点的位置。

图2、CIC滤波器幅频相应

图3显示了差分延迟M对CIC滤波器的影响。从图中可以看到,M除了影响零点的位置,增加M也会对旁瓣衰减产生较大影响,但是通带边沿衰减也较为严重。

图3、差分延迟M对CIC滤波器的影响

图4显示了CIC滤波器速率变化参数R对频率响应的影响。从图中可以看到,随着R的增大,通带边沿衰减加大,旁瓣由一定程度的衰减,但变化不大。从时域来讲,增加R即增加CIC滤波器矩形窗口RM长度。

图4、速率改变因子R对CIC滤波器幅频相应影响

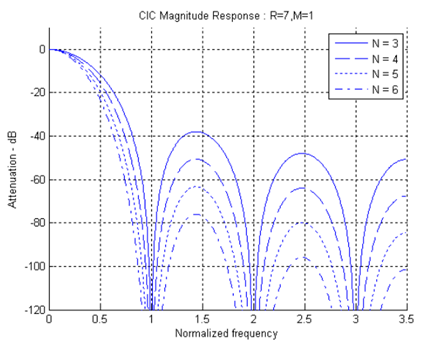

图5显示了改变CIC滤波器阶数N对幅频特性的影响。增加N即增加CIC滤波器级联级数,级联数越大,旁瓣衰减也越大,同时通带边沿衰减也有一定程度增大。

图5、CIC滤波器阶数N对幅频特性的影响

从图3~图5中可以看到,增大M、R及N都能增大CIC滤波器的旁瓣衰减,但对于具体项目应用来说,通常将M及R作为“固定值”,仅通过调整N来改变CIC滤波器旁瓣衰减,以满足滤波器要求。

另外,也可以看到随着N的增加,通带边沿衰减也较为严重,导致CIC通带不平坦加大,对信号带来失真。因此,在使用CIC滤波器时,通常要求设计补偿滤波器(CFIR),主要是补偿CIC滤波器通带衰减,使其通带尽量平坦。

对于补偿滤波器,由于CIC滤波器频率响应具有sinc函数形状,通常补偿滤波器具有反sinc函数形状,如式3所示。

图6显示了补偿滤波器的应用。

图6、CIC补偿滤波器应用

4.2CIC抽取器

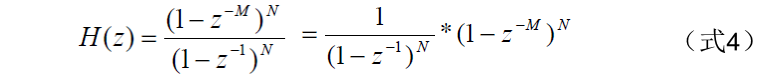

式1中滤波器输出按照R因子抽取后,滤波器fs/R速率下的传递函数表示为式4所示。

该响应可以看做N级积分器和N级梳状器级联,如图7所示。

图7、CIC抽取滤波器结构

从图7中,可以看到,积分器工作在fs采样率,梳状器工作在fs/R速率下,滤波器只有延迟线及加、减法器组成,这有利于硬件实现速率的提高。

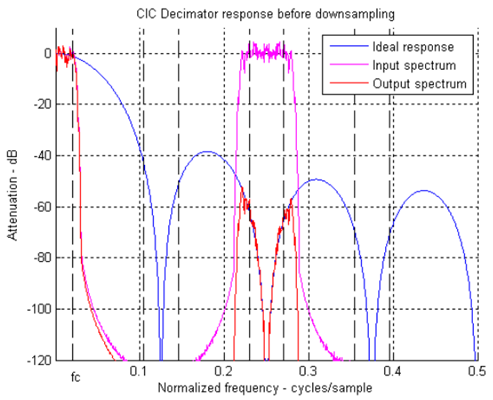

图8显示了抽样前CIC抽取滤波器的响应。当CIC滤波器作为抽取器时,要仔细考虑,抽取后原信号频谱的镜像不能混叠到有用信号fc的通带内。图8中采样速率改变因子R=8,级数N=3,差分延迟M=1。抽取滤波器输入频谱显示在通带(fc=1/32归一化频率)和阻带内(约1/4归一化频率)。抽取器的输出显示了CIC滤波器对输入信号频谱的衰减。图8中垂直虚线显示了抽取时镜像混叠位置,图中归一化频率为高频率(fs)。

图8、抽样前CIC滤波器的幅频响应

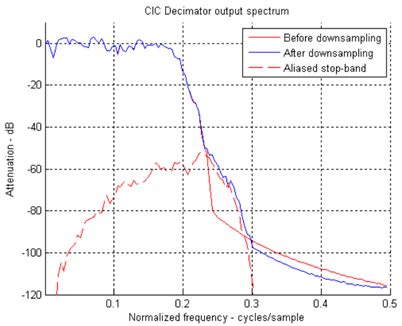

图9显示了CIC抽取器输出影响。在该图中频率轴按照fs/R低频率归一化。

图9、CIC抽取器输出频谱

从图9中可以看到:

1.如果没有混叠发生,图中实红线表示CIC输出频谱;

2.如果由于下采样产生混频,虚红线显示了阻带输出频谱。该混叠频谱影响CIC抽取器最终输出;

3.实蓝线显示了CIC抽取器实际输出,它清楚的显示了下采样中混叠频谱的影响。

因此,必须确保正确选择CIC抽取器参数,以避免混叠对信号频谱噪声影响。

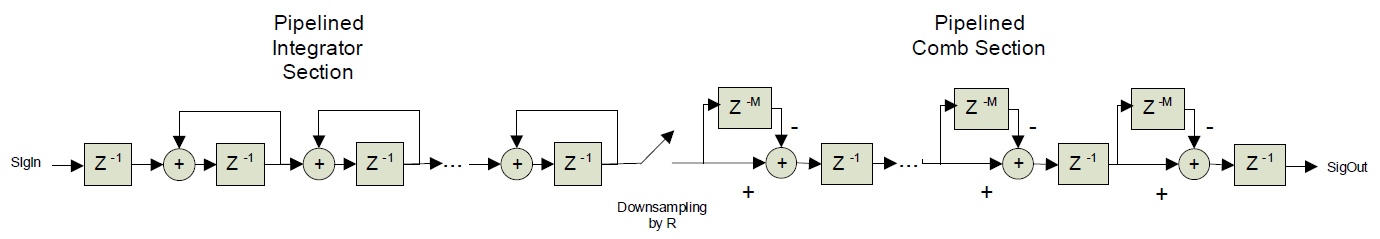

4.2.1 流水线CIC抽取器

为了获得更高的系统时钟频率,CIC抽取器流水线结构可以表示为图10所示。

图9、流水线CIC抽取器结构

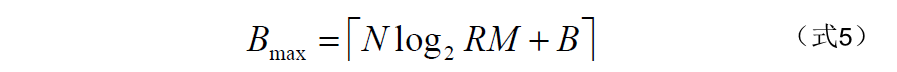

CIC输出数据位宽和设计参数N、M和R有关。全精度CIC抽取输出位宽Bmax可以表示为式5。

为了获得完全的精度,CIC抽取器实现在内部为每个积分器和微分器级使用Bmax位。这在输出端不会引入量化误差。当以量化噪声为代价使用有限精度输出时,CIC抽取器实现中的硬件资源可以减少。这种权衡资源和量化噪声的能力对于实现最佳实现非常重要。

4.3CIC内插器

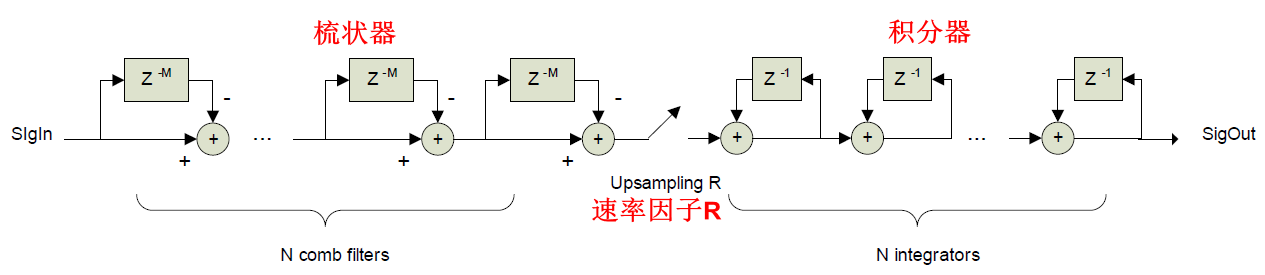

CIC内插器滤波器如图10所示。该结构与CIC抽取滤波器类似,只不过梳状器和积分器的顺序进行了变化。图10中,上采样速率因子R,该速率在梳状器和积分器之间变化,即每个输入采样值间插入R-1个0值。

图10、CIC内插器

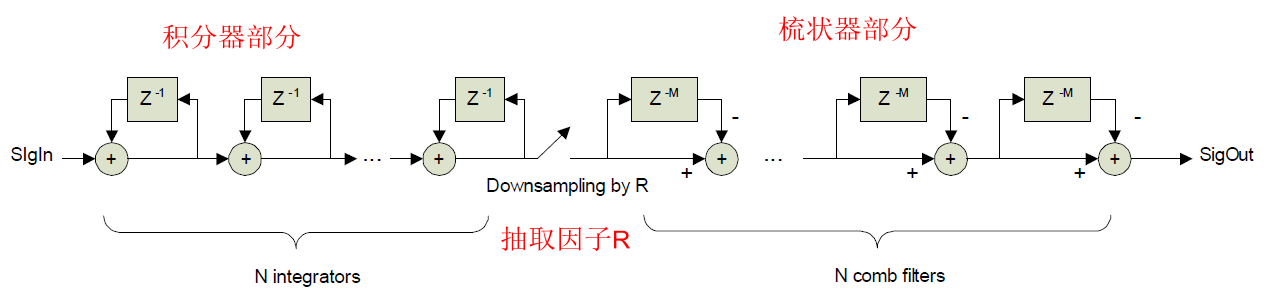

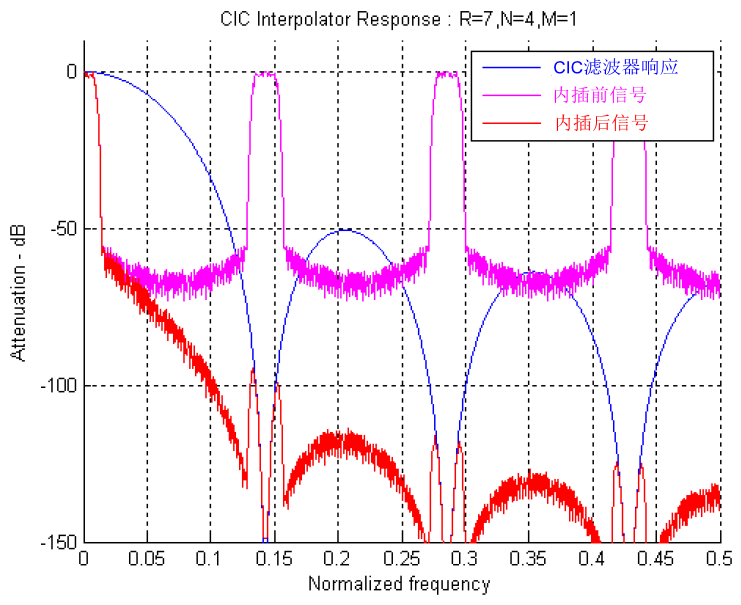

对于内插,CIC滤波器的响应应用于上采样(插入零值样本)输入信号。在速率变化R=7,级数N=4,差分延迟M=1的滤波器中,频率响应如图11所示。

图11、CICI内插器响应

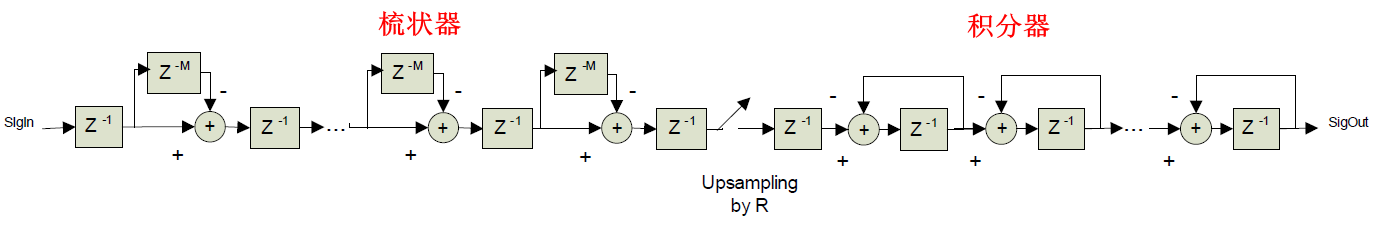

4.3.1流水线CIC内插器

与CIC抽取器类似,CIC内插器流水线结构如图12所示。

图12、流水线CIC内插器

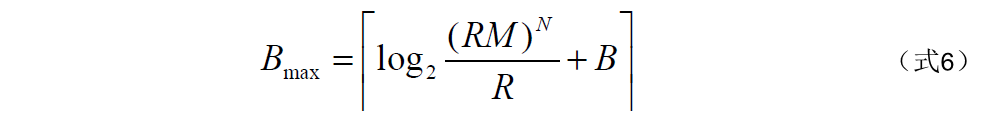

CIC内插器输出数据位宽和设计参数N、M和R有关。全精度CIC抽取输出位宽Bmax可以表示为式6。

滤波器的输出可以选择为全精度或有限精度(带截断或舍入),以适应特定于应用的输出宽度。使用有限精度不会影响内部寄存器的大小,只有末级输出被缩放,如果需要的话,四舍五入以提供所选的输出宽度。

4.3.2输出位宽和增益

如式5和式6所示,CIC滤波器的增益是所有关键设计参数的函数。当输出宽度等于最大寄存器宽度时,IP核输出全精度结果,输出的幅度反映滤波器增益。当输出宽度设置为小于最大寄存器宽度时,输出将被截断,增益相应减小。

当IP核被配置为具有可编程速率变化时,随着滤波器速率的改变,增益也相应地发生变化。当输出被指定为全精度时,随着速率的变化,增益的变化在IP核输出幅度中是明显的。当输出被截断时,IP核移动内部结果,给定当前速率变化的最大值,以完全占用输出位。

4.4CIC滤波器时序描述

CIC滤波器接口采用AXI4-Stream协议进行输入输出数据处理。利用TVALID、TREADY和TDATA信号组合,实现上、下游模块数据流交互,如图13所示。

图13、AXI传输时序图

4.4.1 CIC抽取器时序图

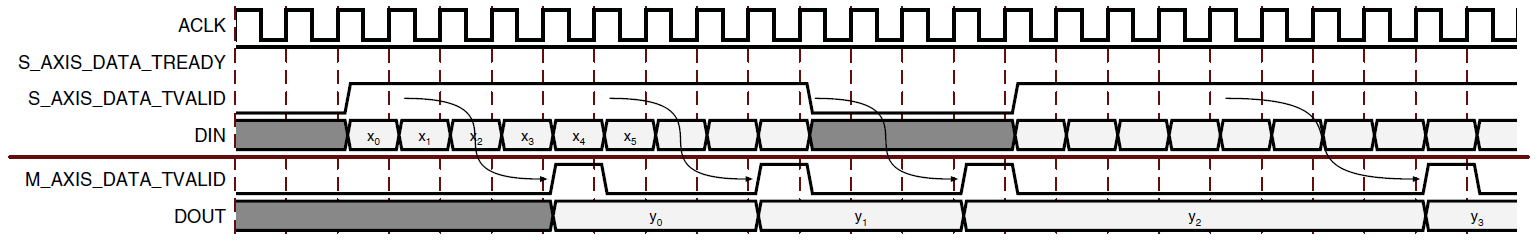

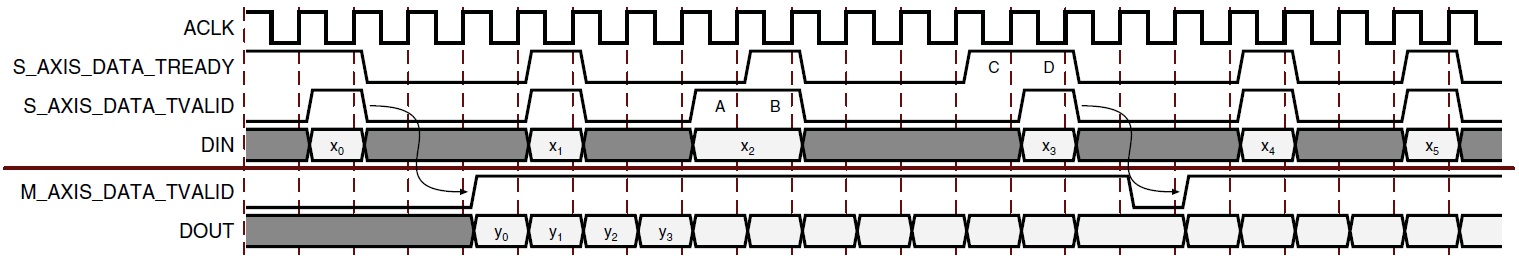

图14显示了下采样因子R=4的CIC抽取器时序图。该IP核未采用过采样,每个时钟上升沿输入一个采样数据。一些时钟后,当m_axis_data_tvalid高电平时,指示第一个滤波输出值可用。该时间间隔和下采样因子R以及内部流水线寄存器设置参数相关。在第一个滤波输出采样值后,后续输出每隔R个时钟周期输出一个滤波数据。

图14、CIC抽取器、固定速率,单通道

图15显示了相同的滤波器,输入采样周期为3。在图中A点波形,CIC IP核准备好接受数据,但是主机未提供。CIC IP核持续询问,直到在B点提供数据。在C点主机在CIC IP核询问前提供了数据,主机持续提供,直到D点CIC IP核可以接收数据。

图15、CIC抽取器、固定速率,单通道,过采样

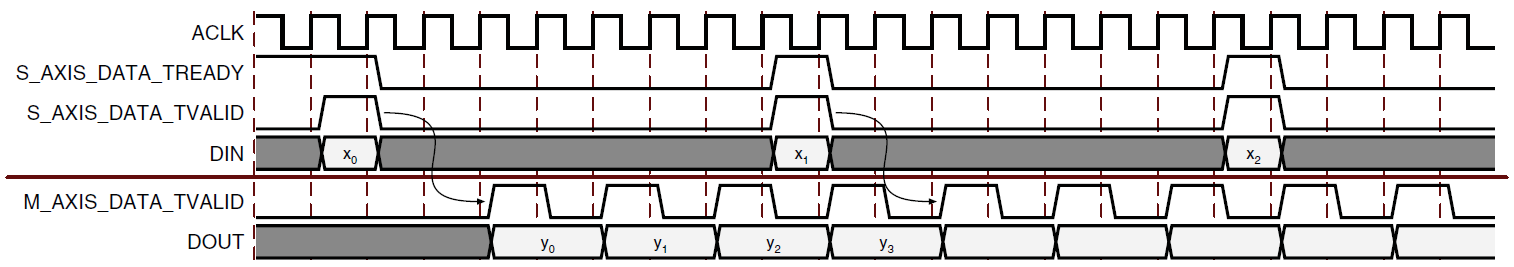

多通道抽取器可以配置为两种模式:数据块模式和数据流模式:

数据块模式:每个数据通道按照背靠背传输,即传输通道N数据后立即传输N+1通道数据;

数据流模式:采样通道在整个多通道周期均匀输出。

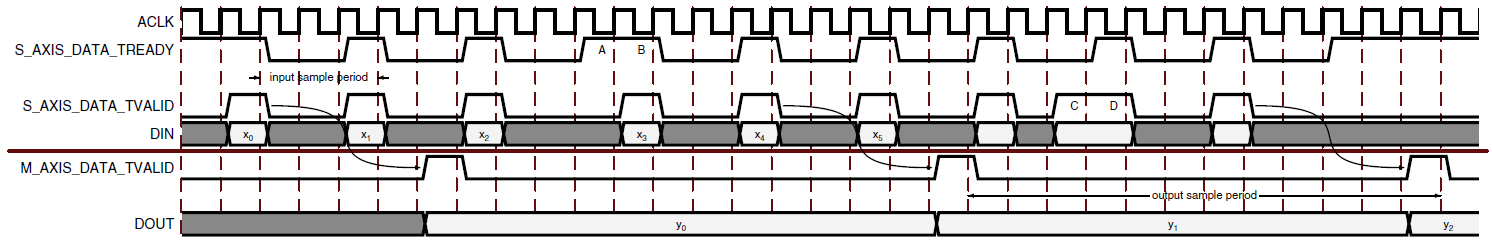

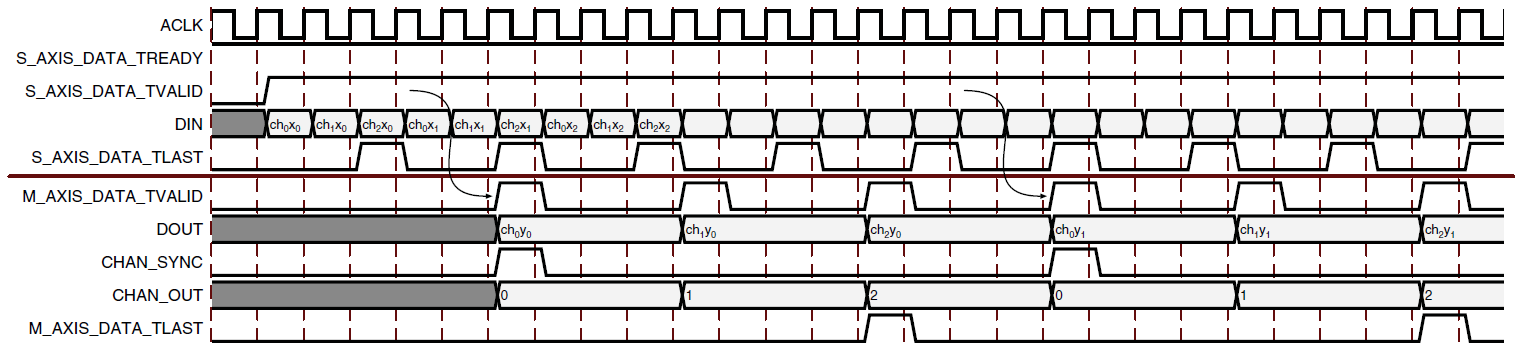

图16显示了R=4时,多通道CIC时序图。在该举例中,抽取滤波器使用数据块模式处理3个通道数据。DIN接口按照时分复用方式输入数据,抽取输出DOUT显示了时分复用数据,CHAN_OUT显示了对应的通道号。

图16、CIC抽取器,固定速率,多通道,数据块模式

图17显示了数据流模式下相同滤波器配置时序图。

图17、CIC抽取器,固定速率,多通道,数据流模式

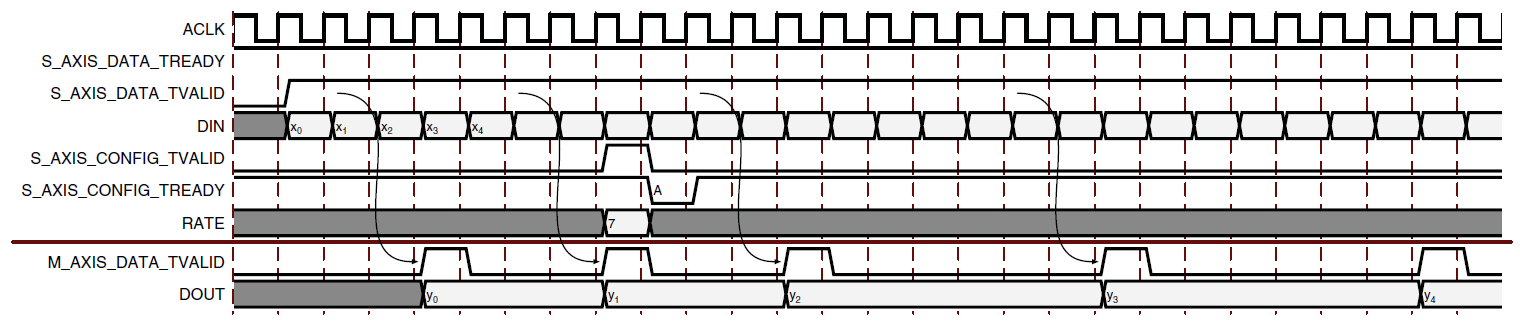

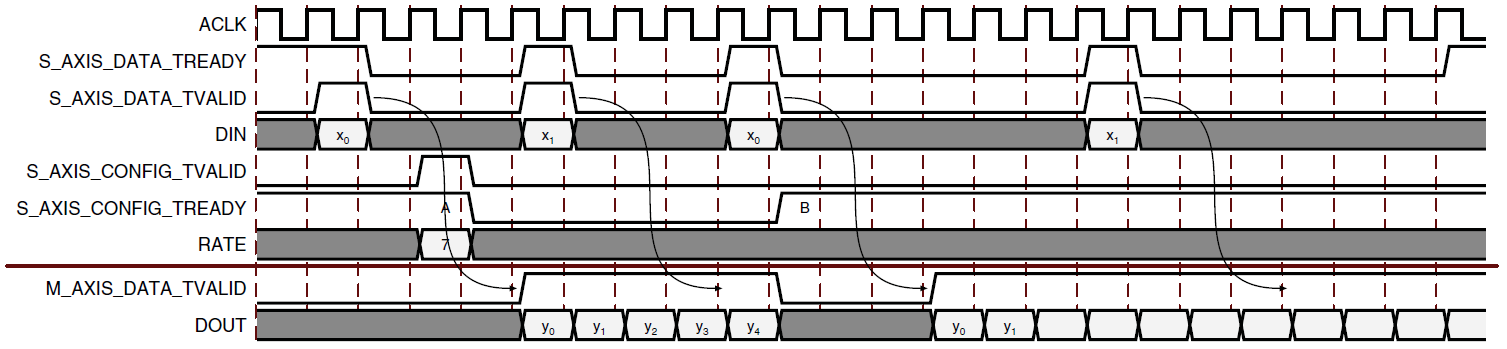

图18显示了CIC抽取器可编程速率时序图。图中抽取器初始下采样率R=4,在一定时间后,下采样率变为R=7。图中A点s_axis_config_tvalid高电平时,指示速率改变可用。CIC IP核在下一采样时钟接收此速率改变,同时,s_axis_config_tready会拉低一个时钟,以防止上游主机插入新的速率改变因子。

图18、可编程速率CIC抽取器

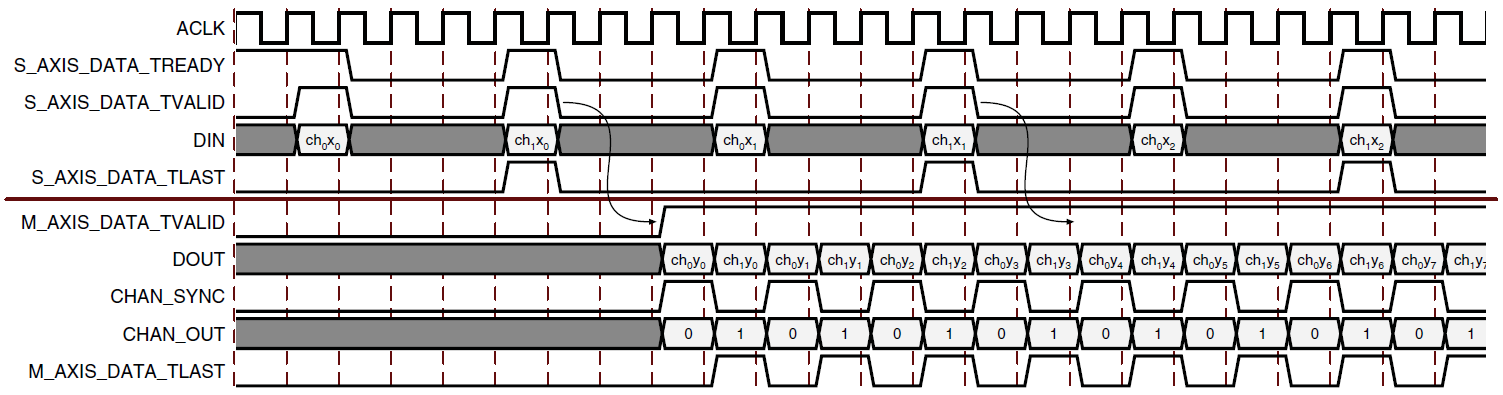

4.4.2 CIC内插器时序图

图19显示了CIC内插器时序图,上采样因子R=4。新的采样数据每4个时钟接收一个。在开始一定延迟之后,m_axis_data_tvalid插入,新的滤波器输出数据在后续每个时钟沿可用。图中A点波形,主机在CIC IP核请求之前提供数据,直到CIC IP核在B点可以接收数据。同样,C点CIC IP核持续请求主机发送数据,主机直到D点提供数据。

图19、CIC内插器,固定速率,单通道

图20显示了相同的滤波器配置,输入采样周期为8的时序图。

图20、CIC内插器,固定速率,单通道,过采样

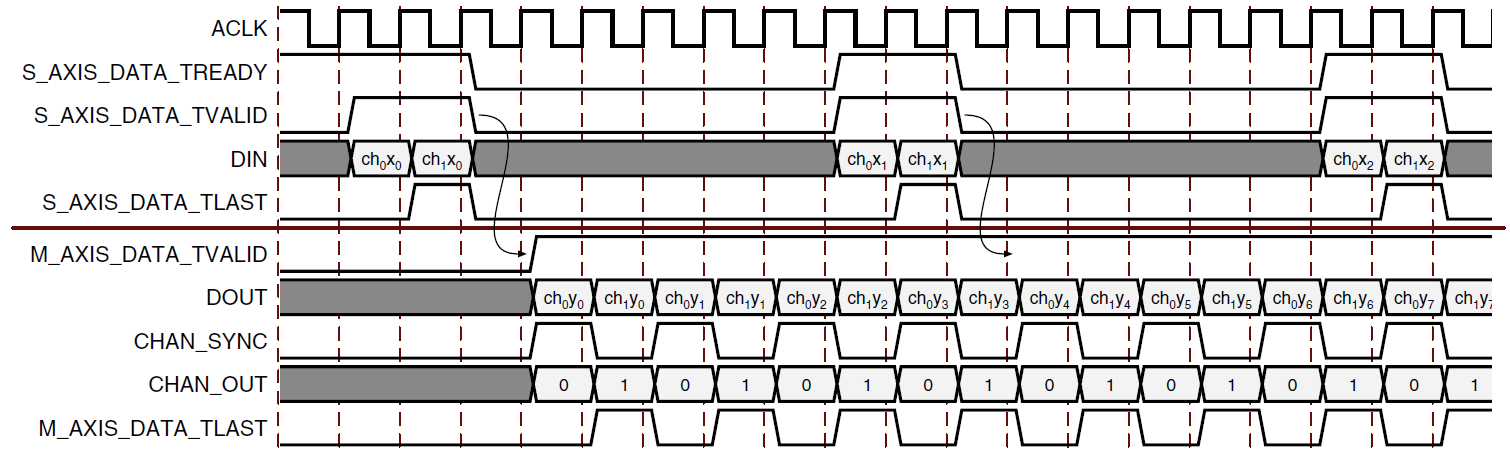

同样,多通道内插器可以配置两种时序模式:数据块模式和数据流模式。

数据块模式:通道数据背靠背传输,即第N个通道传输完后立即传输第N+1个通道数据。

数据流模式:采样通道在整个多通道周期均匀输出。

图21和图22显示了这两种模式时序图。

图21、CIC内插器,固定速率,多通道,数据块模式

图22、CIC内插器,固定速率,多通道,数据流模式

图23显示了CIC内插器采用可编程速率时序图。在该图中,内插器开始采用R=4上采样,一定时间后,R=7。速率改变后,s_axis_config_tready拉低,直到速率R=7已经配置成功。

图23、CIC内插器使用可编程速率