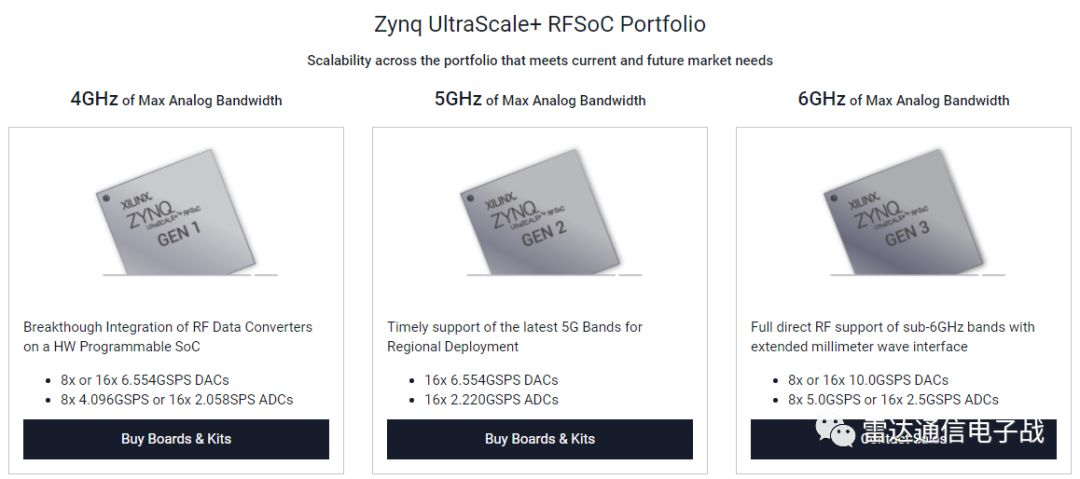

为了使其成为射频系统级芯片,Xilinx公司增加了8个4GS/s采样频率的12位或14位的模数转换器,每个模数转换器都配有可编程数字化下变频器。模数转换器几乎消除了所有的模拟前端组件,射频/中频采样率高达4GHz。

SoC还有8个6.4GS/s采样率的数模转换器,每个数模转换器都配有数字化下变频器。数模转换器在第二奈奎斯特区,以6.554GS/s采样率生成高达4GHz的载波输出频率,包括可编程插补和抽取,并支持双频工作。

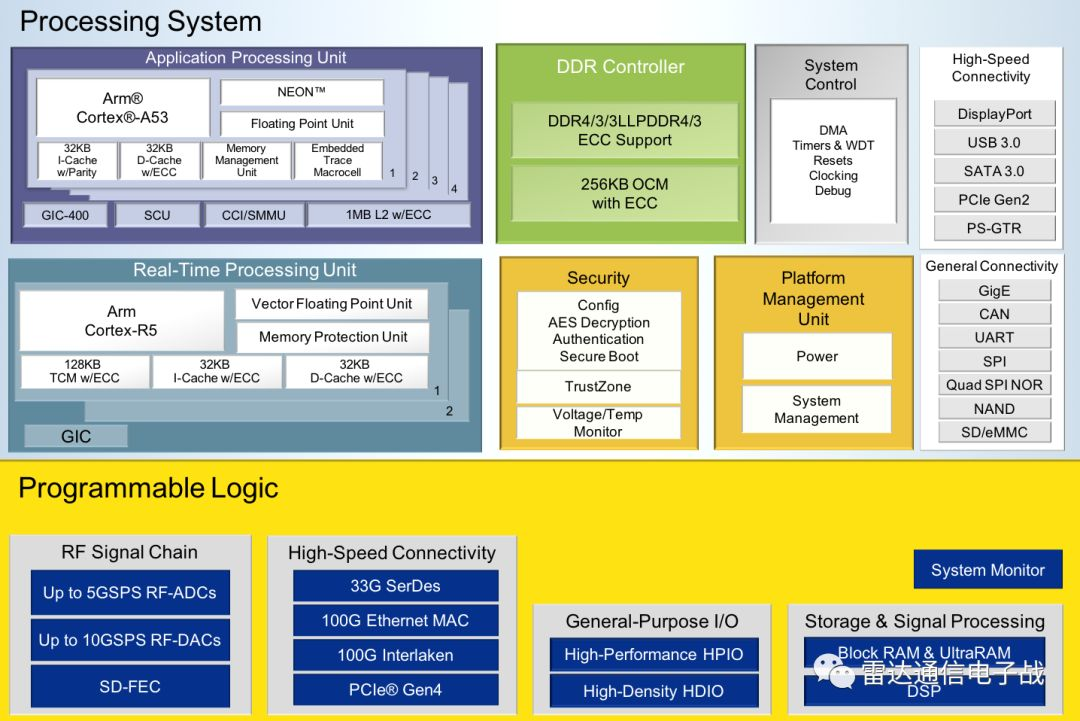

为了连接用于数据或配置存储的外部存储器接口,该处理系统包括DMA、NAND、SD/eMMC和第三代SPI控制器PCIe和100 Gb/s以太网。Interlaken芯片到芯片接口采用高速串行接口,数据传输速率可达150Gb/s。串行收发器的数据传输速率高达28.2Gb/s,采用特高速背板设计,每位的功耗比上一代收发器更低。

SoC还有时钟管理电路,包括时钟合成、阻尼和路由组件,它们共同以最小化偏离、功耗和延迟,提供灵活的时钟分布。通过256位AES-GCM,SHA/384和4096bit RSA模块,可以实现安全引导功能。加密引擎也可用于用户加密。

由于RFSoC通过可编程信号处理,可以实现模数和数模信号转换,因此采用单个芯片或通过一些外部资源实现数字化射频存储器(DRFM)应该是可行的。

至少就目前而言,数字化射频存储器比目前的Zynq UltraScale+ RFSoC更适用于分布式方案。原因之一是第一代芯片的延迟时间为145ns,但是干扰日益复杂的雷达系统所需的往返延迟时间至少为40ns。

另一个原因是数字化射频存储器是自定义子系统,采用专有设计技术、软件和其他技术。因此,分布式方案具有更大的灵活性和差异性,有更好的潜在表现。

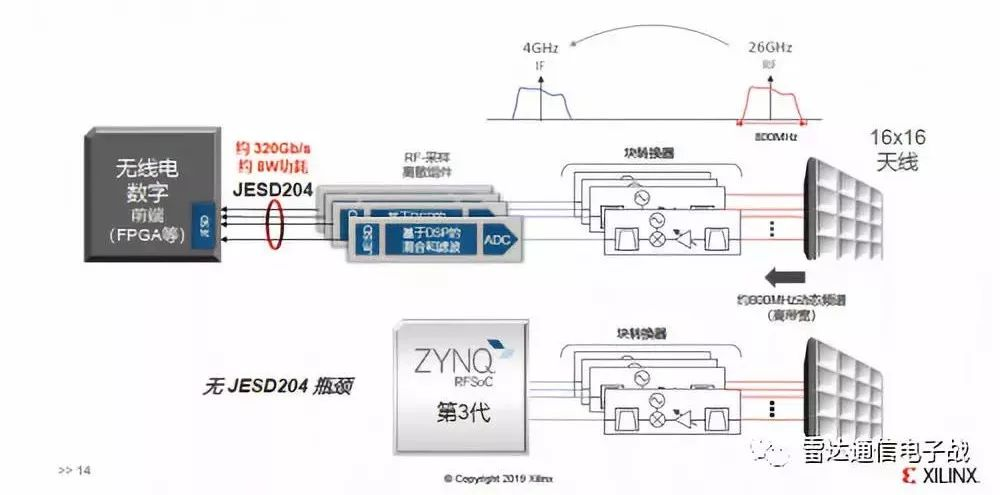

由于模数转换器和数模转换器传统意义上是独立于数字化射频存储器的,所以它们之间需要通过一个高速接口来通信,许多系统采用JESD204B接口,不过这将增加延迟和设计复杂度。

例如,考虑将12位的模数转换器通过并行接口连接到数字化射频存储器,每位由一个低压差分信号(LVDS)表示,与另一对时钟同步信号配对。如果该接口采用双数据率(DDR)技术,那么在一个时钟周期内传输的数据量将增加一倍。Hosking说:“不过,即便采用双数据率,采样频率在1.5GHz以上时会产生大量数据,使低压差分信号(LVDS)不能有效传输到数字化射频存储器。”

为了解决这个问题,可以采用1:2信号分离器形成2个单独的并行接口,每个接口的运行速率为采样率的1/2。因此,以12位模数转换器为例,如果转换器在每12位路径上的采样频率为2GHz,则信号分离器的采样频率为1GHz,低于数字化射频存储器低压差分信号接口适用的最大时钟速率。

但在更高的频率下,模数转换器需要一个1:4信号分离器来保持数据在合理水平。但是在电路板上设计和制造时出现了严重的问题,因为必须非常精确地配对更多信号对,确保从12位发出的数据同时到达数字化射频存储器。

在这种情况下,12位转换器将采用数字化射频存储器上的4组12副引脚(96个I/O引脚和时钟引脚),而数字化射频存储器上通常有400-600个I/O引脚,其中一半引脚只需要连接2个4GHz转换器。

由于电路板上采用了众多技术,它们都需要引脚和信号通道,如果没有适当的地方引接,可能会造成干扰,并降低模数转换器和数模转换器的高动态范围。这样还可能会影响时钟同步、2个在4条28Gb/s通道运行的100Gb/s以太网端口、在8GHz通道运行的第三代PCIe和第三代接口,以及2组DDR4内存。

为解决这一问题制定了JESD204标准,通过数字化射频存储器的千兆位串行接口替代了低压差分信号。大大减少了配对型号的数量,降低了精确匹配跟踪长度的需求。遗憾的是,JESD204标准的4条通道功率约1W,且由于JESD204标准有专门的IP核,使用时必须得到许可。设计的复杂度源自接口的时钟方案,它比并行接口更复杂。

JESD204标准也以其延迟限制而闻名,许多应用程序都无法实现这样的功能。例如,Hosking说:“并行转换器接口可以将数据延迟几个采样时钟周期,但是JESD204标准可以延迟80个采样时钟周期甚至更多,增加了从模数转换器到数字化射频存储器的延迟(对于数模转换器也是同理)。”

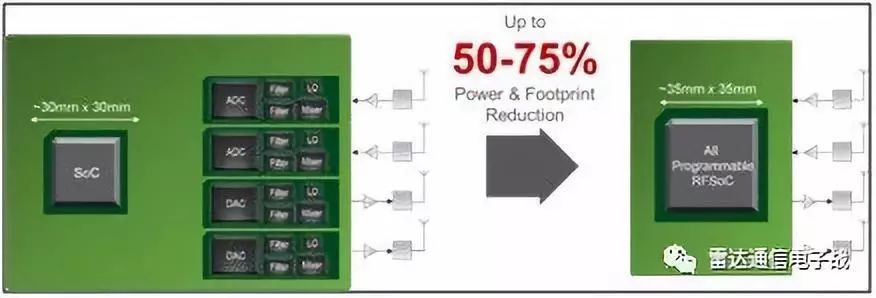

RFSoC在不同程度上解决了这些问题,因为转换器内置在芯片内,与从外部传输信号到数字化射频存储器的方案相比,大大减少了引脚数。这样,数字化射频存储器可以提供更多的通道,因此可以安装更多的设备结构。

RFSoC采用的转换器使用一种称为交织的技术,用500MHz连续时钟脉冲并行生成128位数据,该技术已经使用了一段时间,但也带来了巨大的挑战。Hosking说:“Xilinx公司采用8个500MHz的模数转换器,并使用该方法以4GS/s的速率交织样本,这样非常了不起。”

通过组合多个数模转换器的输出,该交织过程可以获得较高的采样率。高速模数转换器通常在上升沿或下降沿对输入信号进行采样,因此每个时钟周期都有一个采样,模数转换器的采样率和时钟速率相同。