本文转载自:十年老鸟

注:本文由作者授权转发,如需转载请联系作者本人

前言

本文将结合ip example工程来理解transceiver的复位,通过学习记录,力求将其复位过程理解通透。

参考工程为serdes_3g

复位模式

手册中提到了两种复位模式

复位模式

1、顺序模式

2、单步模式

在ip example中,是直接使用顺序模式的,而且手册也是推荐使用顺序模式,那么我们就直接研究顺序模式了,单步模式暂时不关注

//-------------------- Transceiver Reset Mode Operation -------------------- .GTRESETSEL (tied_to_ground_i), .RESETOVRD (tied_to_ground_i),

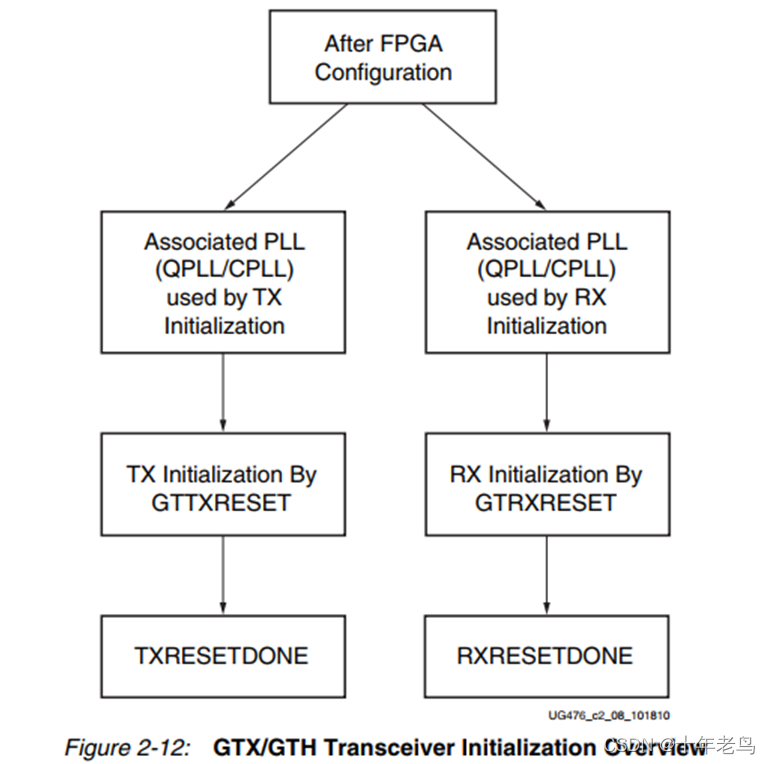

复位的步骤

我们先理解上电过程中,复位的流程是怎么样的。

首先是QPLL的复位,我们顺藤摸瓜首先找到这个模块gtwizard_0_TX_STARTUP_FSM。这个是发射初始化状态机模块。注意,如果有多条lane,会有多个STARTUP_FSM模块。例如例化为:

gt0_txresetfsm_i

gt1_txresetfsm_i

gt2_txresetfsm_i

gt3_txresetfsm_i

尽管每个模块都会有 QPLL_RESET的输出端口,但只有gt0_txresetfsm_i会输出,其他模块会悬空

gtwizard_0_RX_STARTUP_FSM模块的所有例化也有QPLL_RESET端口,但也全部悬空。

既然 提到了这个模块,那我们就先看 gtwizard_0_TX_STARTUP_FSM这个模块

这个模块 STABLE_CLOCK 是主时钟,这是一个freerun的时钟,drp_clk。

主要的启动状态机描述如下:

1、最开始是INIT状态

一开始先计数500ns到init_wait_done拉高,复位状态机才会开始工作。进入ASSERT_ALL_RESETS状态

2、ASSERT_ALL_RESETS:

首先会操作 QPLL_RESET,拉高然后拉低。同时把以下复位控制线置为初始状态。

TXUSERRDY拉低

GTTXRESET拉高

MMCM_RESET拉高

RESET_PHALIGNMENT拉高

RUN_PHALIGNMENT拉低

并且立马进入WAIT_FOR_PLL_LOCK状态。

3、WAIT_FOR_PLL_LOCK:

这里等待WAIT_TIME_MAX个CLK,数满后,进入RELEASE_PLL_RESET状态

4、RELEASE_PLL_RESET:

如果检测到QPLLLOCK(qplllock_sync)为1,则进入WAIT_FOR_TXOUTCLK状态

5、WAIT_FOR_TXOUTCLK:

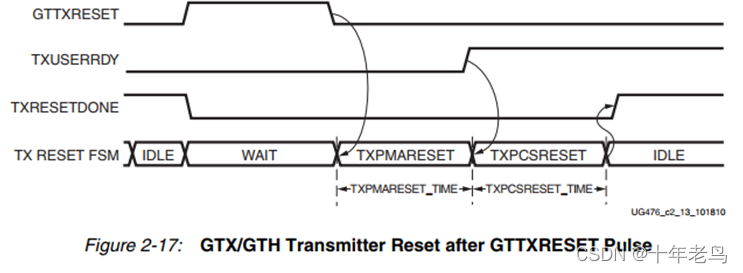

将GTTXRESET拉低。并且等待一段时间后,进入RELEASE_MMCM_RESET

6、RELEASE_MMCM_RESET

MMCM_RESET 拉低,并且等待MMCM_LOCK 拉高。如果MMCM_LOCK 拉高,则进入WAIT_FOR_TXUSRCLK状态。

7、WAIT_FOR_TXUSRCLK

等待一段时间,进入WAIT_RESET_DONE

8、WAIT_RESET_DONE

TXUSERRDY拉高,等待TXRESETDONE拉高,如果TXRESETDONE拉高,则进入DO_PHASE_ALIGNMENT状态。

9、DO_PHASE_ALIGNMENT

RUN_PHALIGNMENT 拉高,等待PHALIGNMENT_DONE 拉高,如果PHALIGNMENT_DONE 拉高,进入RESET_FSM_DONE。

10、RESET_FSM_DONE

TX_FSM_RESET_DONE拉高,表示复位状态机完成。

状态机的等待回应部分都有超时检测机制,如果超时,状态机会回退到ASSERT_ALL_RESETS,继续QPLL_RESET操作。

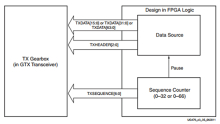

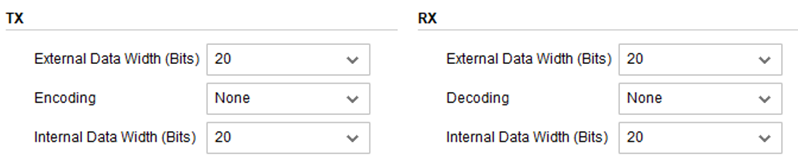

状态机的基本功能分析完毕,由于我们这里实际设置

不存在数据位宽的变化,因此并不存在并不存在MMCM_RESET和RUN_PHALIGNMEN等操作,

实际上有用的端口为:

QPLL_RESET: 拉高然后拉低

QPLLLOCK:高电平锁定

GTTXRESET:初始态为高,拉低释放复位

TXRESETDONE

TXUSERRDY

TX_FSM_RESET_DONE

总之,首先是检测QPLLLOCK,QPLL锁定后,才会对TX transceiver进行初始化复位,控制管脚为GTTXRESET和TXUSERRDY

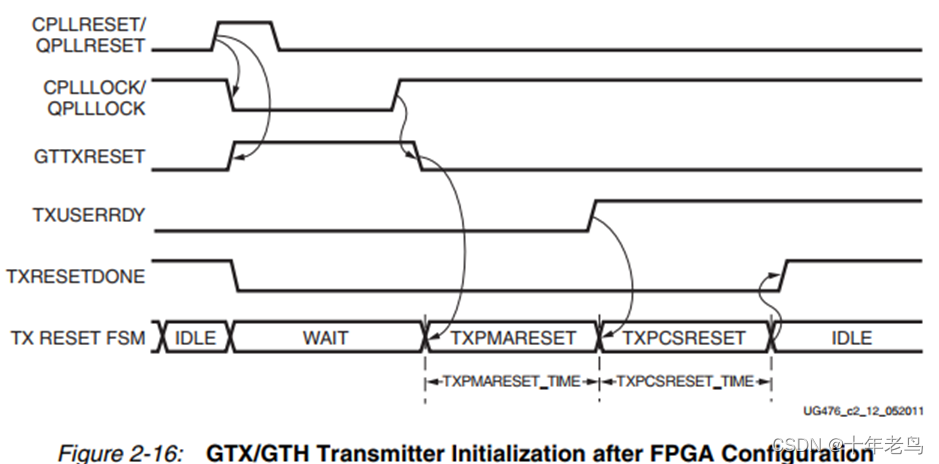

这就是这个模块的时序图了。

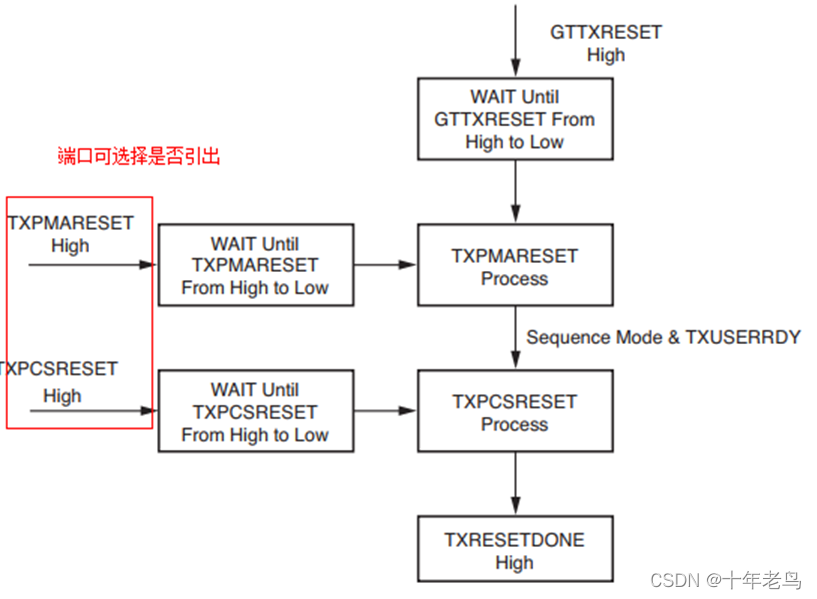

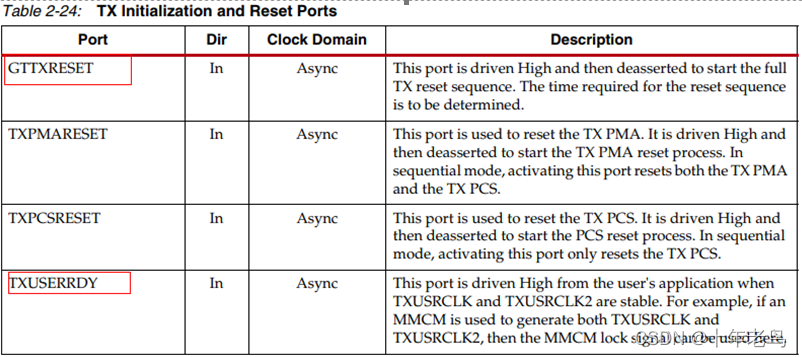

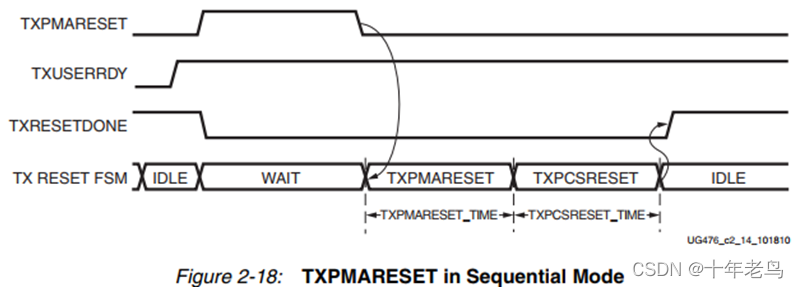

那我们知道GTTXRESET就是对TX链路进行复位的操作,直到TXRESETDONE表示复位过程结束,其中间是有哪些操作呢

中间 包含TXPMARESET和PCSRESET的过程

TX的顺序复位必须满足一下条件:

1、 GTRESETSEL在顺序模式下必须为低

2、 GTTXRESET必须要使用

3、 TXPMARESET 和TXPCSRESET在TXRESETDONE检测为高之前必须恒定为低

4、 GTTXRESET不能拉低,除非QPLL锁定

如果FPGA加载过程中GTX复位模式默认为顺序模式,在配置完成后,QPLLRESET和GTTXRESET可以被置位在等待最少500ns后。

默认模式为单步模式的情况我们不考虑,也不会使用。

GTX和GTH收发器允许用户使用GTTXRESET高脉冲复位整个TX链路

TX PMA和TX PCS也可以单独复位。GTTXRESET 必须恒定为0,在TXPMARESET和TXPCSRESET过程期间。

驱动TXPMARESET从高到低开启PMA复位过程,TXPCSRESET必须恒定为低在TXPMARESET过程期间。在顺序模式下,复位状态机将自动开启PCS复位在完成PMA复位后,如果TXUSERRDY为高的话

驱动TXPCSRESET从高到低开启PCS复位过程当TXUSERRDY为高的情况下。TXPMARESET必须恒定为低当PCS在复位过程中。在顺序模式下,复位状态机仅仅复位PCS

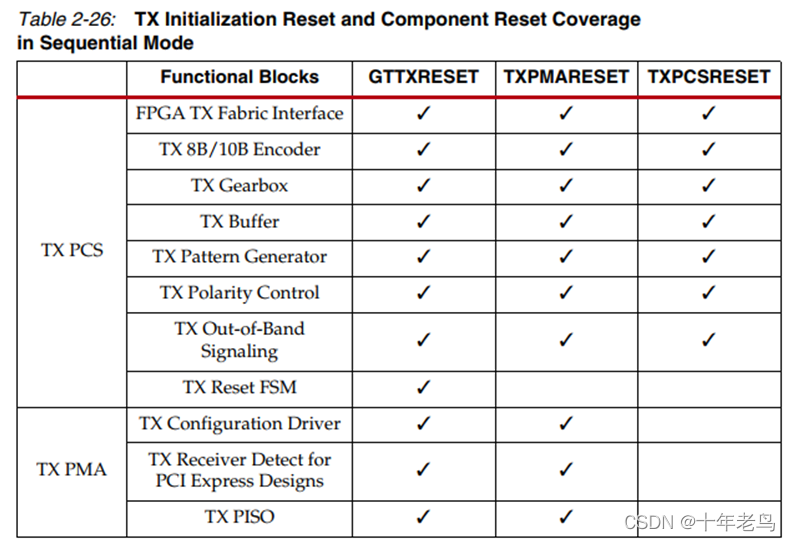

下面的表格总结了所有用于GTX/GTH收发器和组件的复位在顺序模式下。使用TXPMARESET在顺序模式下基本上覆盖了GTTXRESET的所有功能除了TX复位状态机

顶层使用

为了实际操作尽量简化,我们实际上不使用TXPMARESET、和TXPCSRESET这两个接口。如果要复位,使用GTTXRESET即可。

1、 soft_reset_tx_in,这个复位会Reset QPLL,并且gtwizard_0_TX_STARTUP_FSM这个状态机模块也会重置。使用这个复位整个serdes全部都会复位,(不管收发)

2、 gt0_gttxreset_in/gt1_gttxreset_in/gtN_gttxreset_in 这些复位,就是只复位各个lane的TX了

.gt0_gttxreset_in (tied_to_ground_i), 这个端口可以印出来可配置,这就是每条lane的GTTXRESET复位

那我们通过哪个信号来指示txlane已经准备就绪,可以使用了呢。

gtwizard_0_TX_STARTUP_FSM模块中的TX_FSM_RESET_DONE信号,也即

顶层的gt0_txfsmresetdone_i,这个为高了,表示serdes已经准备好了。

gt0_txusrclk2_i 作为时钟(这里gt0_txusrclk_i和gt0_txusrclk2_i是同一个信号)

gt0_txfsmresetdone_i作为复位信号