本文转载自:FPGA打工人微信公众号

Abstract Shell刚推出不久,局限性还是蛮大的,首先工具必须是vivado2020.2版本及其以上,器件目前只支持UltraScale+。Abstract Shell最大的优势是除第一次外,后续可以减少bit的生成时间,只包含必要的最小的逻辑和物理资源,可以做到:

减少每次RM编译的运行时间和内存使用量(第一次除外);

减少每个RP的静态设计的checkpoint大小;

对于有多个RP的设计,可以并行编译;

生成部分bit时不需要加载完整的静态设计;

隐藏静态设计中存在的专有信息。

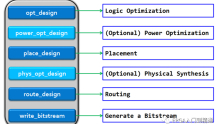

Abstract Shell毕竟来源于DFX,所以流程几乎相同,差异仅限于从初始(父)实现编译静态设计checkpoint的步骤,以及打开静态设计开始为每个RP实现第二个或者更多RM的步骤。

首先需要先过一遍DFX的Flow,之后会得到实现后的checkpoint,以这个checkpoint为基础,为每个RP创建新的shell,后续这些RP可独立处理。

Abstract Shell运行暂时不支持project模式,但可以初始的project可以通过Vivado IDE得到。

打开完整routing的初始checkpoint,每个RP都会有一个RM,通过write_abstract_shell命令为目标RP创建一个Abstract Shell。

write_abstract_shell -cell <arg> [-force] [-quiet] [-verbose] <file>

会发现checkpoint比原来routing的checkpoint要小,至于小多少,可能具体情况具体讨论。每个RP是独立管理的,所以每个RP彼此可以并行实现。

当route_design完成时,调用write_checkpoint来保存整个抽象Shell和实现的RM,并调用和write_checkpoint -cell来单独保存实现的RM。可以将RM的checkpoint单独读入完整的静态设计checkpoint(如果有必要,还可以将其他RP的RM检查点读入),以组装一个完整的设计。

bit的生成有两种方式。第一种是使用标准的DFX方法, 此处重点说第二种,第二种是直接从任何RM的Abstract Shell实现生成部分bit,此方法不需要完整的静态设计的checkpoint来生成部分bit。具体命令如下:

write_bitstream -cell <cell_inst> <RM_partial>.bit

注意的是-cell不能省略,否则会报错。

当然,最直观的当然需要一个flow,下一篇将自己做的实验Demo介绍一哈。