本文转载自:十年老鸟的CSDN博客

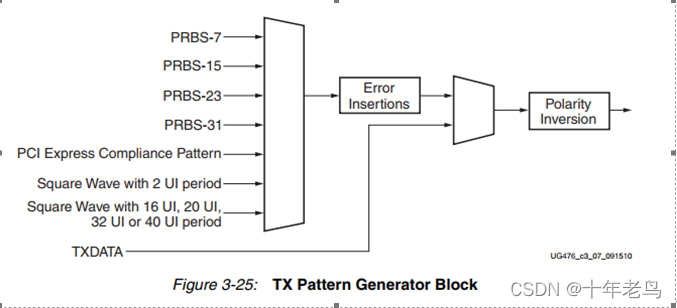

PRBS测试序列

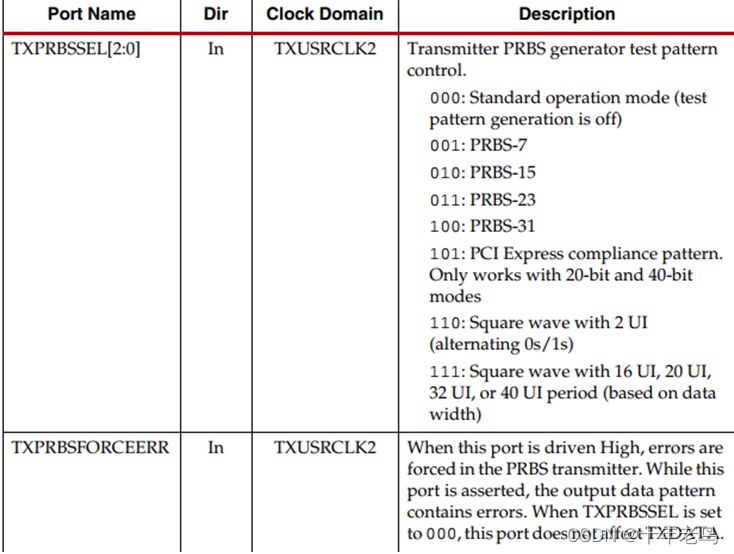

TX部分:

看这个图基本就一目了然了。这个和ibert界面的选择测试序列功能是可以对应上的。

包含4中PRBS码以及FAST CLK和SLOW CLK。

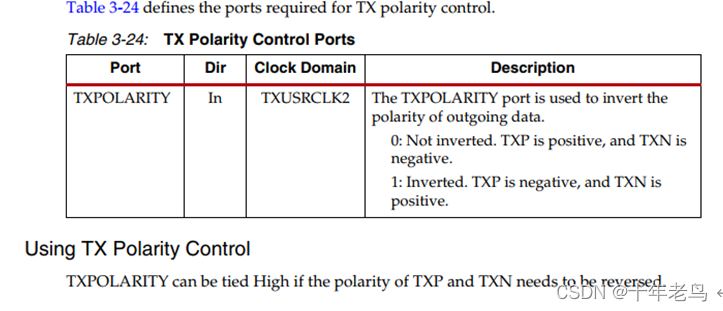

其次还要注意Polarity Inversion,之前我碰到一个项目,是Intel平台和Xilinx平台的互相测试误码,结果死活不对。结果发现Polarity Inversion这个极性要取反。应该是两端硬件P/N连线反了的原因。

总之调试的时候如果没问题没关系,有问题的时候这个地方需要留意一下

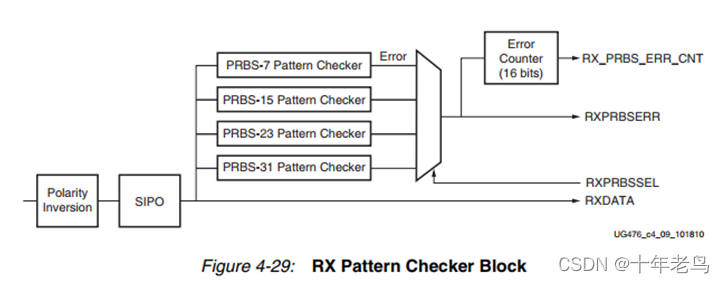

RX部分:

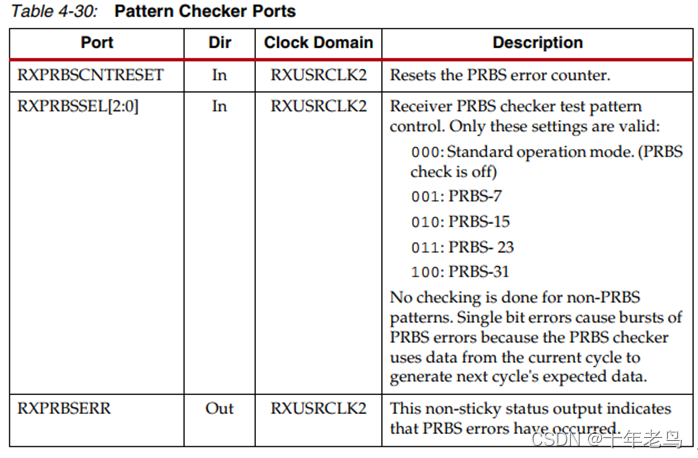

主要控制端口如下:

分别是选择码型,误码计数复位、有误码指示。

如果还想知道误码个数,那么必须通过DRP地址来访问。

因为用的不多,而且用起来也比较简单,这里就不多说了。

RX Equalizer (DFE 和LPM)

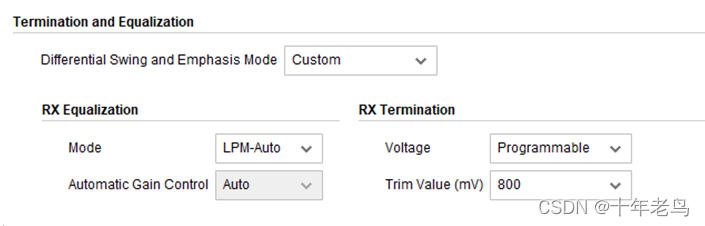

在IP核的这个页面,存在着如下两个配置:

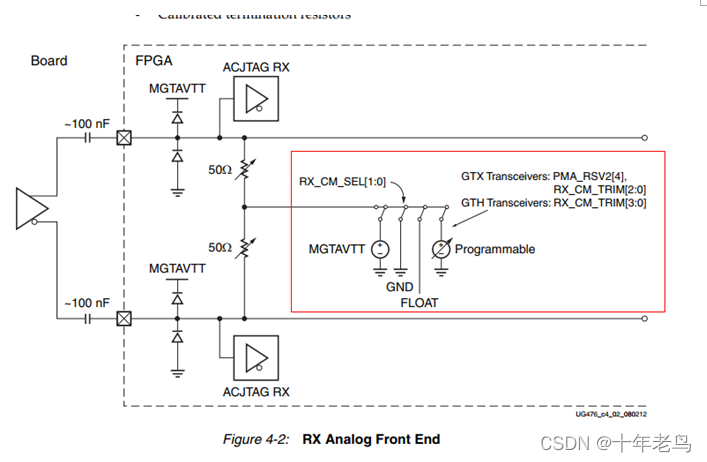

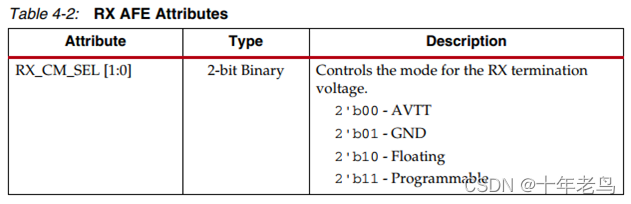

1、 RX Termination Voltage (接收端电压)

可以配置成4种状态

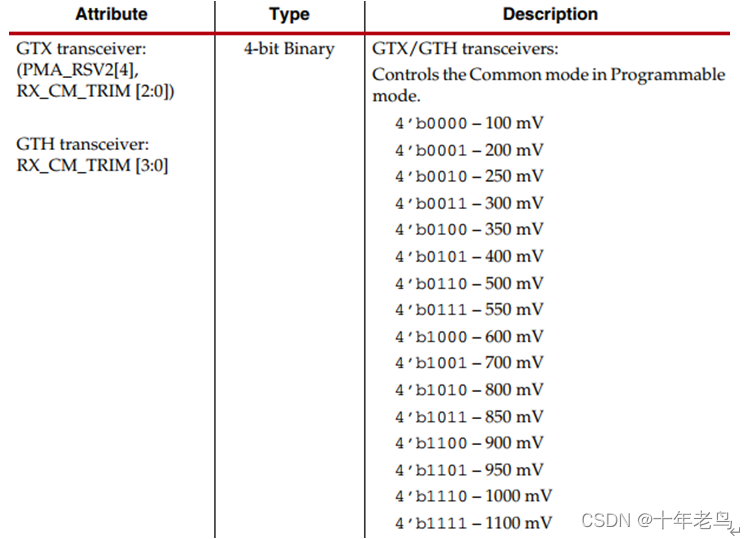

其中,如果配置成programmable的话,还需要配置电压:

这两个配置IP核没有显性端口引出可以直接配置,只能通过DRP总线接口进行配置。

一般来说使用默认的即可,严谨一些的话可以通过扫眼图来确定哪个参数最好。

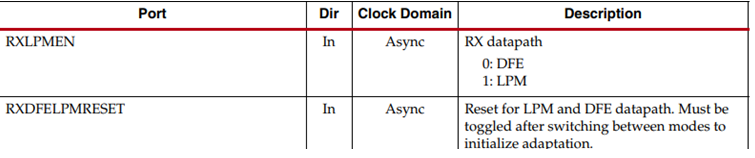

2、RX Equalization Mode (接收端均衡模式)

还有一个需要进行配置的就是使用DFE模式还是LPM模式。

一般来说,我们实际使用都是LPM模式(之前FAE建议的),至于这些东西深层次的原理也不是太清楚。

主要就是RXLPEN这个端口。

可以看出这些端口或者参数在IBERT上都是可以对应上的。

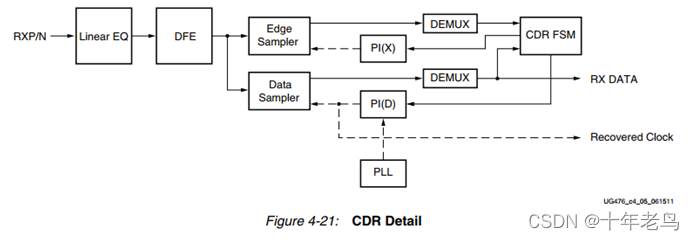

RX CDR

关于RX CDR这里也提两嘴,具体的原理就不再阐述了,结果就是在高速数据中提取边沿来恢复时钟,以及两边沿中间采样恢复数据。如下图所示,本质上也是一个锁相环,它需要CPLL或者QPLL来产生一个本地时钟做为参考,通过CDR状态机能够跟踪与本地时钟有若干频偏的的输入信号流。

注意图中的Recovered Clock仍然还是串化时钟,RX DATA 仍然是串化数据。

以前我一直以为会有一个CDRLOCK的显示指示,后面发现没有。

手册中虽然提到了这个RXCDRLOCK信号,但却处于保留状态。后面看看高阶点的FPGA有没有这个指示信号

1、这里还有一个最开始搞transceiver犯迷糊的问题。我们叫恢复时钟,那如果RX/PN没有输入时,恢复时钟Recovered Clock是不是没有时钟输出么?

也有的,即便RX/PN没有输入,Recovered Clock依然会有输出。也就是说这个Recovered Clock的源头实际上本地产生的,只是在有RX/PN输入数据时,CDR 锁相环会将本地时钟与数据包含的时钟无限逼近。这里是我自己的理解,参考了我之前做数字锁相环的一点认知,不敢保证完全符合实际。但需要知道的是:RX/PN没有输入,Recovered Clock依然会有输出。

2、 是否可以以这个恢复时钟作为我们FPGA整个工程的系统时钟呢?

不行,尽管上面说了恢复时钟不管RX/PN有没有信号都有时钟输出,但只有在RX/PN有信号输入且锁定的时候会是稳定的。RX/PN没有信号输入时,经过恢复时钟的频率与期望的频率仍然也是接近,但必然存在频偏以及抖动,而FPGA系统时钟必须要是稳定的。因此,一般来说,我们使用transceiver的接收数据时,一般都会和恢复时钟与本地时钟做跨时钟域处理,然后用本地时钟作为系统时钟来处理数据。这样即便是transceiver异常的时候,系统时钟也还是稳定的。

以上同样参考了我之前做数字锁相环的一点认知,也不敢保证完全符合实际,但技术应该是相通的,应该八九不离十吧。

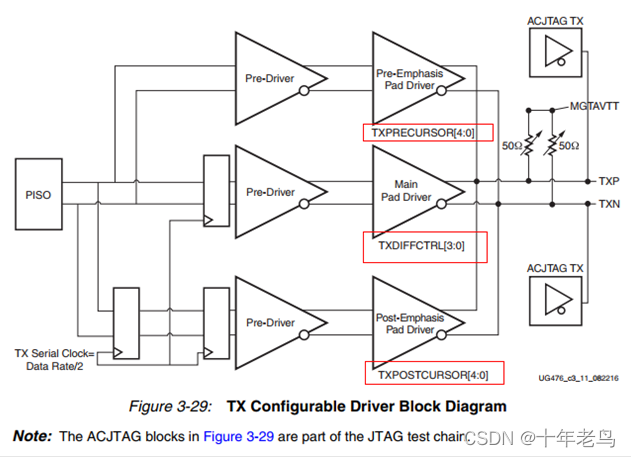

TX Driver

TX端则简单很多,不再详细阐述。我们主要关注的是TXDIFFCTRL 摆幅、Pre-Emphasis 预加重、Post-Emphasis 去加重,这三个参数。这三个参数可以使用默认参数,严谨一点可通过ibert通过扫瞄眼图的方式确定一个最优参数。