本文转载自:Vuko-wxh的CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

写在前面

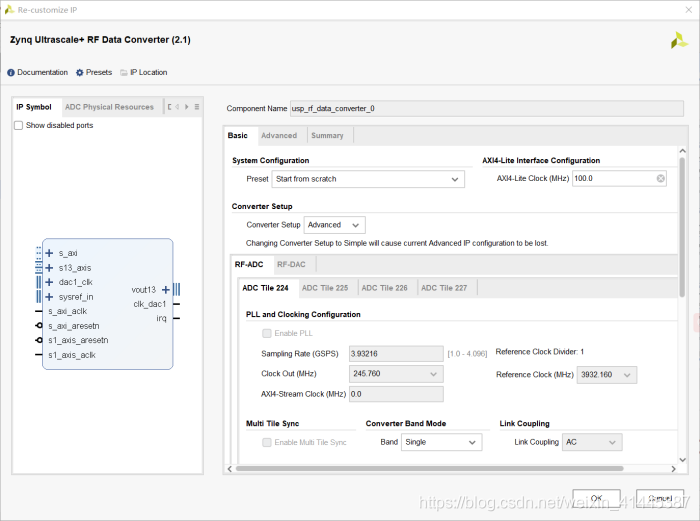

承接前文,本文是射频数据转换器IP使用介绍的第二篇,参考PG269的第五章,完成对射频数据转换器(RF Data Converter)IP配置界面的相关参数进行详细的说明,以便于后续开发设计进行查阅。

IP基础配置

Presets (预配置)

Vivado IDE IP核心配置界面提供了一种保存和应用预设配置的方法。从预设菜单,几个固定配置是可用的。

4×4: ADC:R2C DAC:C2R : 4个RF-ADC和4个RF-DAC启用。RF-ADC采用real to I/Q模式配置。RF-DAC配置为I/Q to real模式。

8×8: ADC:R2C DAC:C2R :8个RF-ADC和8个RF-DAC启用。RF-ADC采用real to I/Q模式配置。RF-DAC配置为I/Q to real模式。

ADC:R2C Multi x 2 DAC: C2R Multi x2 :RF-ADC配置在 x2多波段使用实转虚的数据。RF-DAC配置在 x2多波段使用虚转实的数据。

ADC:C2C Multi x 2 DAC: C2C Multi x2 :rf - adc配置在x2多频带使用虚到虚的数据。RF-DAC配置在 x2多频带使用虚到虚的数据。

DAC: C2R Multi 2x2 :在单个RF-DAC 块上的 2x2多频段使用虚到实的数据。

DAC: C2C Multi 2x2 :在单个RF-DAC 块上的 2x2多频段使用虚到虚的数据。

DAC: C2C Multi x4 : 在单个 RF-DAC 块上的 1x4 多频段使用虚到实的数据。

除了这些固定的预置外,还可以通过选择“保存”来保存当前配置,配置…从预设菜单。保存配置后,可以通过选择Apply configuration …随时重新加载配置。

System Configuration (系统配置)

预设配置:此菜单允许用户从预定义配置列表中选择,以避免手动输入所有设置。

Converter Setup(变频器的设置)

转换器设置菜单为设置IP配置提供了高级(Advanced )和简单(Simple)的选项。

Advanced : 所有片都是独立配置的。

Simple: 用户可以看到单个RF-ADC和RF-DAC块的配置选项。设置好片配置信息后后,通过从给定的片列表中选择片,就可以将RF-ADC配置应用到设备中的任何RF-ADC。类似地,RF-DAC配置可以应用于任何RF-DAC片。

可以在不丢失配置信息的情况下从简单设置更改为高级设置。但是,从高级到简单是不可能的。只支持向下兼容。

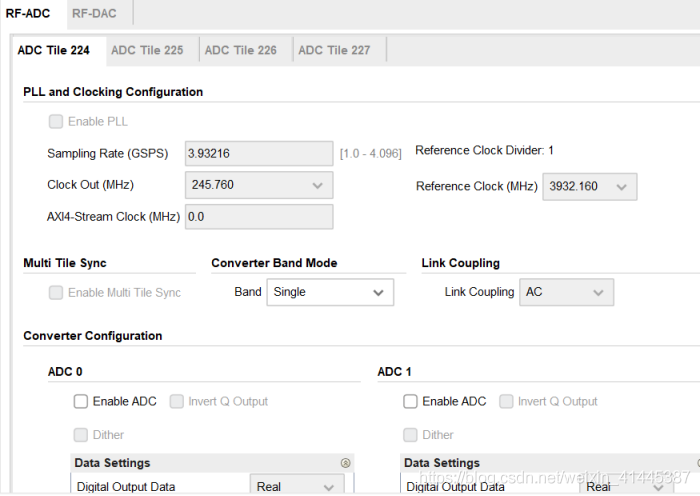

RF-ADC片配置

这些参数对片中的每个RF-ADC都是通用的。

Link Coupling (链路耦合): 这决定了RF-ADC的输入信号是交流耦合还是直流耦合。典型的应用程序 使用 交流耦合 ,但对于某些应用程序(如Zero IF),也支持直流耦合。当选择直流链路耦合模式时,外部驱动电路的共模电压需要使用外部驱动的VCM引脚(参见RF-ADC模拟输入)与RF-ADC内部的共模电压对齐。 VCM引脚 只能用于 直流耦合模式 ,如果选择交流耦合模式,则可以保持浮动。

Converter Band Mode(转换器频带模式): 每个RF-ADC可以独立工作(单频带模式),也可以与其他转换器一起工作(多频带模式)。以下模式可用于RF-ADC。

Single: 转换器工作在单频带模式。

Multi x2 (pair 01): ADC 0 的输出通过 ADC 0 和 1 的 DDC 通道路由。数字设置,例如混频器模式和类型,可用于每个 DDC 通道。 在 Quad 器件中,tile 中的其他两个 RF-ADC 在单频带模式下运行。

Multi x2 (pair 23): 这个选项类似于前面的模式。在这里,ADC 2的输出被路由到DDC通道2和3。瓦片中的其他转换器以单频带模式工作。此选项仅在Quad设备上可用。

Multi x2 (both): 来自 ADC 0 的数据为 DDC 通道 0 和 1 提供输入。来自 ADC 2 的数据为 DDC 通道 2 和 3 供电。此选项仅适用于四通道器件。

Multi x4: 片中的所有DDC通道都来自ADC 0。此选项仅在Quad设备上可用。

Multi Tile Sync(多片同步): 启用后,块包含在多片同步组中。 RFADC Tile 0 必须启用并与被配置为启用此选项的 tile 的转换器 0 一起出现在组中。

RF-ADC转换器配置

common

Enable ADC(启用ADC): 选择是否启用所选片内的所选转换器。取值为TRUE和FALSE。

Invert Q Output (Q逆变输出): 只有在选择I/Q输出数据且开启微调混频器时才能设置。当设置时,混合器的求积输出为负。这允许生成-Q数据。

Dither (抖动): 选择所选片是否启用了抖动。抖动应启用,除非采样率低于0.75倍的RF-ADC的最大采样率。

Bypass Background Calibration (Gen 1 and Gen 2) 旁路背景校准(第 1 代和第 2 代): 如果选中,则在 IP 逻辑中而不是在 RF-ADC 中实现背景校准逻辑。 该驱动程序可用于将一组固定的校准系数下载到 IP。 此选项仅在 Real input to Real output 模式下可用,并且对抽取模式和每个 AXI4-Stream 周期的样本数有进一步的限制。

Enable TDD Real Time Ports (Gen 3)启用 TDD 实时端口(第 3 代): 启用后,tdd_mode 端口将添加到 IP。 这可以通过关闭 RF-ADC 的部分来实现节能。

Data Settings

Digital Output Data (数字输出数据): :设置所选片内所选转换器的数据类型。该参数仅在启用转换器时可配置。有效值为Real和I/Q。当转换器0被设置为I/Q时,转换器1也必须被启用;当转换器2被设置为I/Q时,转换器3也必须被启用;否则配置无效。

Decimation Mode(抽取模式): 设置所选片内所选转换器的抽取值。 该参数仅在转换器启用时可配置。 从下拉菜单中选择值 1x、2x、3x、4x、5x、6x、8x、10x、12x、16x、20x、24x、40x。 当转换器未启用时,该值为关闭。第 1 代/第 2 代值为 1x、2x、4x 和 8x。

Samples per AXI4-Stream Word(每AXI4-Stream的采样字数): 设置每个周期的字数。 当特定转换器已启用时,此参数是可配置的。 有效值介于 1 和 12 之间,可以使用下拉列表进行选择。 取值范围取决于所选的采样率,以将 AXI4-Stream 时钟保持在规范范围内。 所需的 AXI4-Stream 时钟是 IP 核的输入,并显示基于所选总线宽度的值。

Observation Channel (Gen 3)(观测通道(第三代)): 启用并设置观测通道。

启用ADC观测通道端口:启用给定RF-ADC的tdd_obs端口。还为观测通道添加了一个AXI4-Stream接口。

抽取模式:设置所选转换器在所选贴图内的观测通道的抽取值。该参数仅在开启观测通道时可配置

Samples per AXI4-Stream Word(每AXI4-Stream的采样字数): 设置每个周期的字数。 当特定转换器的观察通道已启用时,此参数是可配置的。 取值范围取决于所选的采样率,以将 AXI4-Stream 时钟保持在规范范围内。 所需的 AXI4-Stream 时钟是 IP 核的输入,其值基于选定的总线宽度显示。

Mixer Settings

Mixer Type(混频器类型): 设置要使用的混音器类型。有效的选项有bypassed, coarse, and fine。可选择的选项取决于转换器数字输出数据字段的选择。

Mixer Mode(混频器模式): 设置所选转换器的混合器模式。该参数仅在启用转换器时可配置。混频器模式的选择取决于混频器类型和所选数字输出数据的格式。当真实数据输出时,混频器被绕过。当I/Q数据输出混频器可以设置为 real 的I/Q或I/Q到I/Q。

Coarse Mixer Frequency (粗混频器频率): 设置粗混频器的频率。 混频器类型选择为粗调时,此参数可配置。有效选项为 Fs/2、Fs/4 和 -Fs/4。

Fine Mixer Frequency (细混频器频率): 设置细混频器的频率。此参数仅在选择fine作为混合器类型时有效。有效频率范围为- 10GHz ~ 10GHz。

Fine Mixer Phase(细混频器相位) :设置细混频器的相位。此参数仅在选择fine作为混合器类型时有效。有效范围是-180到180。

Analog Settings

Nyquist Zone(奈奎斯特区): 选择偶数和奇数奈奎斯特区操作。

Calibration Mode(校准模式): 根据输入信号的特性选择不同的校准优化方案。自动模式(第3代)适用于所有输入频率。模式1是最佳输入频率Fsamp/2(Nyquist)±10%。模式2是输入频率输出的最佳范围。

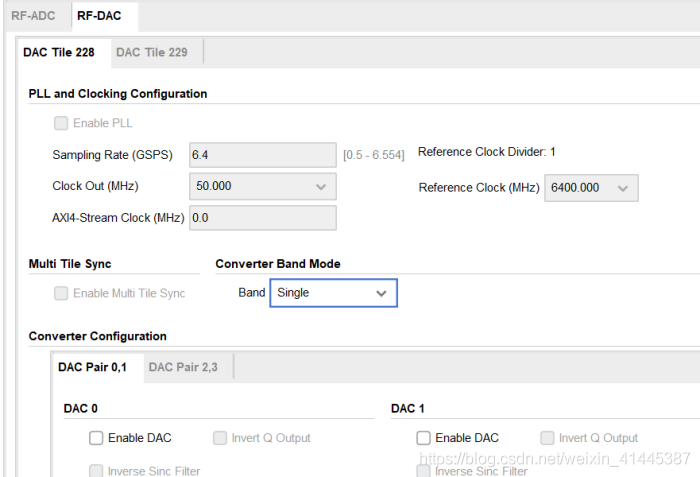

RF-DAC片配置

这些参数对一个tile中的每个RF-DAC都是通用的。

Converter Band Mode(转换器频带模式): 每个 RF-DAC 可以独立运行(单频段模式)或与片中的其他转换器一起使用(多频段模式)。 以下模式是可用于 RF-DAC。

Single: 转换器工作在单频带模式。

Multi x2 (pair 01): DUC通道0和1驱动DAC0的输入。每个DUC通道都有数字设置,如混频器模式和类型。片中的其他两个rf - dac工作在单频模式。

Multi x2 (pair 23): 这个选项类似于前面的模式。DAC2是由DUC通道2和3驱动的。片中的其他转换器以单频带模式工作。

Multi x2 (both): 之前的多频段选项的组合。 DAC0 转换来自 DUC 通道 0 和 1 的数据。 DAC2 由 DUC 通道 2 和 3 驱动。

Multi x4: DAC0接受来自tile中的所有DUC通道的数据。

Multi Tile Sync(多片同步): 启用后,块包含在多片同步组中。 RFDACTile 0 必须启用并与被配置为启用此选项的 tile 的转换器 0 一起出现在组中。

Variable Output Current (Gen 3)(可变输出电流(第3代)): 当可变输出电流模式启用时,输出电流按照DC和AC Switching中的规定设置。DAC_AVTT必须设置为3.0V。

Link Coupling (链路耦合): 这决定了 RF-DAC 的输出信号是交流耦合还是直流耦合。 在直流耦合模式下,共模电压是固定的。 在此模式下,VOP 范围会减小。

RF-DAC转换器配置

common

Enable DAC(启用DAC): 选择是否启用所选片内的所选转换器。取值为TRUE和FALSE。

Invert Q Output(Q逆变输出): 当使能时,转换器的Q输出被反转。仅当勾选“I/Q输出数据”时可设置。后续的模拟混频器必须实现减法,I x cos(f) - Q x sin(f) ,因此提供一个-Q信号(负正交)的选项,以便外部混频器可以执行加法,I x cos(f) + (-Q)sin(f)

Inverse Sinc Filter(Sinc逆变滤波器): 选择是否启用Sinc逆变滤波器。该参数仅在启用转换器时可配置。取值为TRUE和FALSE。这适用于两个Nyquist区域,基于模拟设置→Nyquist区域选择。

Enable TDD Real Time Ports (Gen 3)启用 TDD 实时端口(第 3 代): 启用后,tdd_mode 端口将添加到 IP。 这可以通过关闭 RF-DAC 的部分来实现节能。

Data Settings

Digital Output Data (数字输出数据): :设置所选片内所选转换器的数据类型。该参数仅在启用转换器时可配置。有效值为Real和I/Q。当转换器0被设置为I/Q时,转换器1也必须被启用;当转换器2被设置为I/Q时,转换器3也必须被启用;否则配置无效。

Decimation Mode(抽取模式): 设置所选片内所选转换器的抽取值。 该参数仅在转换器启用时可配置。 从下拉菜单中选择值 1x、2x、3x、4x、5x、6x、8x、10x、12x、16x、20x、24x、40x。 当转换器未启用时,该值为关闭。第 1 代/第 2 代值为 1x、2x、4x 和 8x。

Samples per AXI4-Stream Word(每AXI4-Stream的采样字数): 设置每个周期的字数。 当特定转换器已启用时,此参数是可配置的。 有效值介于 1 和 12 之间,可以使用下拉列表进行选择。 取值范围取决于所选的采样率,以将 AXI4-Stream 时钟保持在规范范围内。 所需的 AXI4-Stream 时钟是 IP 核的输入,并显示基于所选总线宽度的值。

Datapath Mode (Gen 3) 数据路径模式(第3代): 选择RF-DAC数据路径模式。以下选项是可用的。这些模式适用于数字数据路径,可以使用模拟设置->奈奎斯特区域选择来在第一或第二奈奎斯特区域输出该数据。

DUC 0 to Fs/2: 全奈奎斯特DUC模式。

DUC 0 to Fs/4: 使用低通IMR滤波器的半奈奎斯特DUC模式。

DUC Fs/4 to Fs/2: 使用高通IMR滤波器的半奈奎斯特DUC模式。

No DUC 0 to Fs/2: DUC旁路模式。

Mixer Settings

Mixer Type(混频器类型): 设置要使用的混音器类型。有效的选项有bypassed, coarse, and fine。可选择的选项取决于转换器数字输出数据字段的选择。

Mixer Mode(混频器模式): 设置所选转换器的混合器模式。该参数仅在启用转换器时可配置。混频器模式的选择取决于混频器类型和所选数字输出数据的格式。当真实数据输出时,混频器被绕过。当I/Q数据输出混频器可以设置为 real 的I/Q或I/Q到I/Q。

Coarse Mixer Frequency (粗混频器频率): 设置粗混频器的频率。 混频器类型选择为粗调时,此参数可配置。有效选项为 Fs/2、Fs/4 和 -Fs/4。

Fine Mixer Frequency (细混频器频率): 设置细混频器的频率。此参数仅在选择fine作为混合器类型时有效。有效频率范围为- 10GHz ~ 10GHz。

Fine Mixer Phase(细混频器相位) : 设置细混频器的相位。此参数仅在选择fine作为混合器类型时有效。有效范围是-180到180。

Analog Settings

Nyquist Zone(奈奎斯特区): 选择偶数和奇数奈奎斯特区操作。

Decoder Mode(解码模式): RF-DAC解码器可以优化为低信噪比或高线性度。

系统时钟配置

AXI4-Lite接口配置

AXI Clock Frequency (MHz): 核心需要关于AXI4-Lite时钟输入频率的信息,以确保RF-ADC和RF-DAC块的上电顺序的正确计时。时钟的速度应该以兆赫为单位输入。

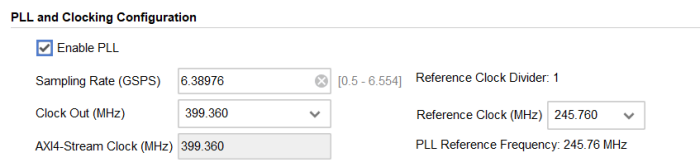

片时钟设置

采样率和时钟频率在本节中设置。这些设置由片中的每个转换器共享。

Sampling Rate(GSPS): 设置每个片的采样率。当片中至少有一个转换器被启用时,它是可配置的。有效值取决于所选的设备和包。

Max Fs (GSPS) :给出了每个片的最大采样率以供参考。

PLL: 选择是使用还是屏蔽片中的 PLL。 当片中的至少一个转换器被启用时,它是可配置的。 如果需要使用 RFdc 驱动程序 API进行动态重新配置 PLL,则必须在 Vivado IDE 中启用 PLL。 有效值为 True 或 False。

Reference Clock (MHz): 设置片的时钟输入频率。它是可配置时,锁相环和至少一个转换器在tile是启用的。它的值取决于tile的采样率。给出了一个基于所选抽样率的值的下拉列表。为了获得最佳的相位噪声性能,建议在锁相环输入处使用正确的参考频率。

PLL Reference Clock: 设置频率的PLL输入时钟,如果PLL是为一个特定的tile启用。

Reference Clock Divider: 参考时钟分频器,设置锁相环参考时钟输入上的分配器。

Fabric Clock (MHz): 这是在所选片的AXI4-Stream时钟输入上提供的时钟频率。所需的频率由采样率和转换器配置中的设置决定。因为一个片上的所有AXI4-Stream端口共享一个公共的AXI4-Stream时钟,所以片上的所有转换器配置必须要求相同的时钟频率。

Clock Out (MHz): 设置片上输出时钟的频率。这个时钟可以用来驱动AXI4-Stream时钟输入。当tile中至少有一个转换器被启用时,它是可配置的。这些值取决于tile的采样率。给出了一个基于所选抽样率的值的下拉列表。

Clock Source (第3代): 设置每个片的时钟源。对于只有双RF-DAC的第3代设备,每个启用RF-DAC的时钟源必须设置为偶数块。

Distribute Clock (第3代): 设置片是否将分配时钟到设备上的其他片。

off : 不进行分配时钟。

Input Refclk: 当 PLL 启用时,输入参考时钟从 tile 转发。如果 PLL 未启用,则分配输入采样时钟。

PLL Output: 当PLL 被启用时,来自 PLL 的时钟输出从tile转发。

锁相环概要设置

PLL 摘要提供有关已启用 PLL 的频率和分频器设置的信息。

Vco(MHz): 压控振荡器的频率。

Fb Div: 反馈分频器设置。

M: 输出分频器设置。

R: 参考时钟分频器设置。

高级配置

RF Analyzer: 射频分析仪提供硬件测试系统。系统包含为这个IP核实例配置的数据刺激和捕获块。

PL Clock Frequency (MHz): 如果选择多片同步,则必须提供PL时钟和向系统发送PL SYSREF。为了准确的SYSREF捕获,频率必须是RF-ADC和RF-DAC AXI4-Stream时钟的普通整数倍。

RF-ADC

Enable Real Time Ports: 使能RF-ADC Over Threshold、Over Voltage、Over Range和pl_event端口。

Enable Cal Freeze Ports: 使能校准冻结逻辑。当模拟输入过压或相关的int_cal_freeze输入被断言时,校准被冻结。

Auto Cal Freeze: 自动校准冻结。如果选择此选项,除了手动校准冻结过程之外,当模拟输入超出范围时,校准将被冻结。

Enable Real Time NCO Ports: 启用实时 NCO 端口。可以实时修改 DDC 中混频器 NCO 的频率和相位。 选择此选项可启用 RF ADC 的实时 NCO 接口。

Enable Real Time Digital Step Attenuation Ports (Gen 3): 启用实时数字步进衰减端口(第 3 代)。如果选择此选项,则可以通过实时 DSA 信号接口更改数字步进衰减器设置。

RF-DAC

Enable Real Time Ports: 启用RF-DAC Fast Shutdown和pl_event端口。

Enable Real Time NCO Ports: 在DUC中,混频器的频率和相位可以实时修改。选择此选项将启用RFDAC的实时NCO接口。

Output Current: 选择20 mA和32 mA的RF-DAC输出电流。在20ma模式下,DAC_AVTT等于2.5V。在32ma模式下,DAC_AVTT等于3.0V。

Variable Output Current Mode (Gen 3)可变输出电流模式(第3代): 当可变输出电流模式关闭时,输出电流由输出电流选项设置。 在 20 mA 模式下,DAC_AVTT 等于 2.5V。 在 32 mA 模式下,DAC_AVTT 等于 3.0V。 启用可变输出模式后,可以通过 RF-DAC 选项卡中的可变输出电流字段在每个片的基础上设置输出电流。 DAC_AVTT设置为 3.0V。

Enable Real Time Variable Output Power Ports (Gen 3): 启用实时可变输出电源端口(第3代),如果选择此选项,则会为每个启用的 RF-DAC 添加实时 VOP 信号接口。 这使得能够实时更新输出功率。

references

PG269 Zynq UltraScale+ RFSoC RF Data Converter