本文转载自:FPGA技术实战的CSDN博客

引言:本文我们继续介绍FPGA收发器TX结构和功能。通过文本你可以了解一下内容:

TX 8B/10B编码器结构和使用

TX Gearbox功能介绍

TX 差分管脚极性控制

1.TX 8B/10B编码器

PCIe、SRIO、STAT等高速串行协议数据发送都采用了8B/10B编码方案,它是一种行业标准编码方案。8B/10B以每字节(8bits)两比特的开销来换取DC直流平衡,来确保时钟可以从数据流中正确恢复。如图1所示,GTX/GTH收发器内置8B/10B TX路径实现TX数据编码,无需消耗FPGA逻辑资源。

图1、GTX/GTH收发器TX内部结构(点击看大图)

使能8B/10B编码会增加TX路径上数据延迟,如果不需要,可以旁路8B/10B编码,以减少TX路径延迟。

1.1 8B/10B比特和字节顺序

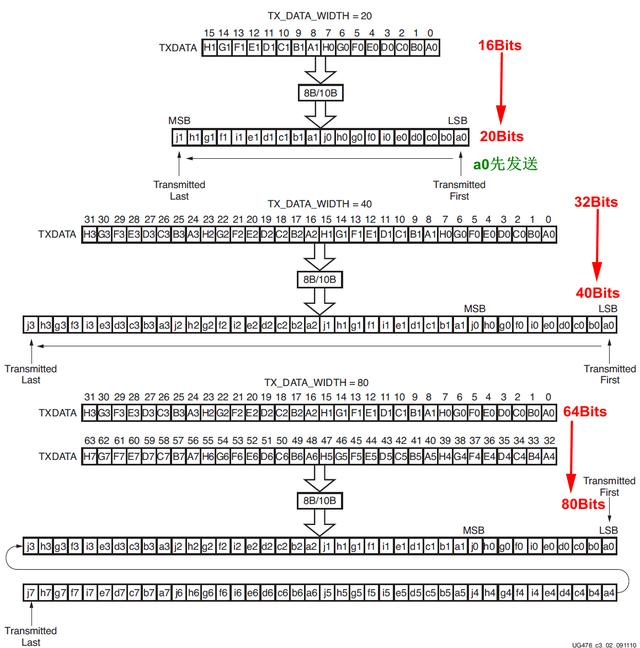

图2显示了收发器TX 8B/10B编码流程。8B/10B是否使能会影响FPGA TX接口TXDATA的数据格式,这一点我们在上一节内容中有详细描述。

图2、收发器TX 8B/10B编码流程

8B/10B编码器要求a0比特先发送,GTX/GTH收发器优先发送最右侧比特。因此为了匹配8B/10B编码,GTX/GTH收发器内部的8B/10B编码器自动翻转发送数据比特。

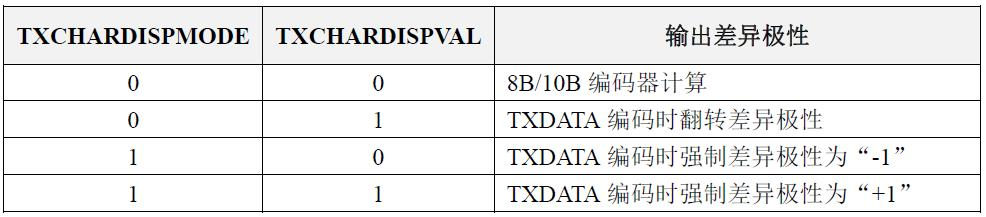

1.2 K字符和差异极性控制

8B/10B编码表使用特殊的字符(K字符)用作控制功能。TXCHARISK端口用来指示TXDATA端口的数据是否为K字符。8B/10B编码器检查接收到的TXDATA字节,如果匹配为K字符,则TXCHARISK比特为置为高。

图3、差异极性控制

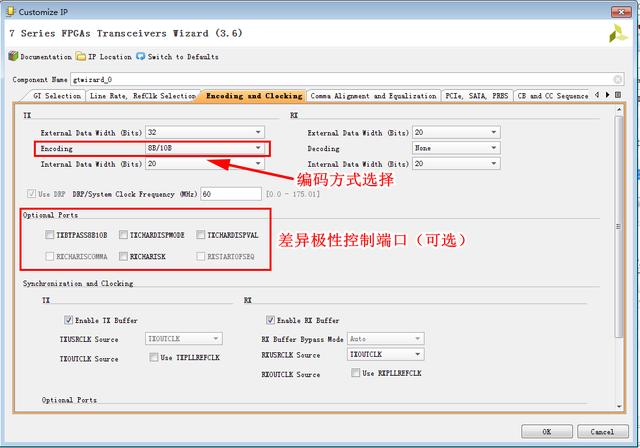

由于8B/10B是直流平衡的,所以发送“1”和“0”的个数比例应该为1:1,为了实现这一要求,编码器总是计算发送“1”和“0”之间的差值。每发送一个字符后,这种差值要么为“+1”,要么为“-1”,这种不同被称为“运行差异”。GTX/GTH收发器允许控制这种差异极性,如图3所示。图4举例了8B/10B编码方式选择及差异极性控制选择GTX/GTH IP核界面。

图4、编码方式及差异极性控制配置界面

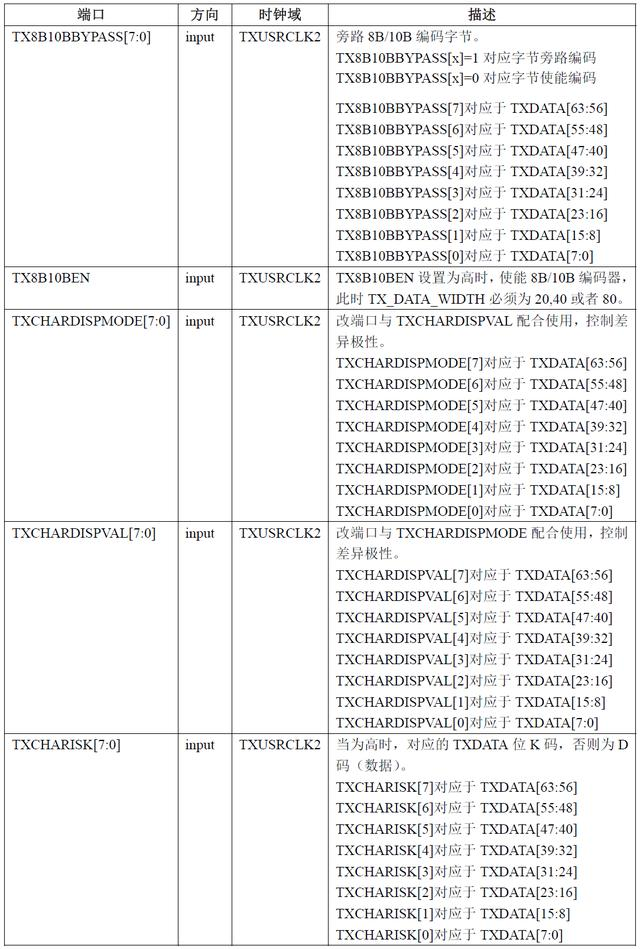

1.3 8B/10B端口(Port)定义

图5、8B/10B编码器端口定义

2.TX Gearbox(速率变换箱)

图1中②为TX Gearbox在GTX/GTH收发器结构中的位置。一些高速数据速率协议使用64B/66B编码来减少8B/10B编码的开销,同时保留编码方案的优点。TX Gearbox提供了对64B/66B和64B/67B编码支持。常见的高速协议Interlaken就采用了64B/67B编码方案。TX Gearbox支持2字节、4字节和8字节接口定义,数据加扰是在FPGA逻辑内实现的。在GTH收发器中,CAUI接口模式支持附加的TX Gearbox特性。

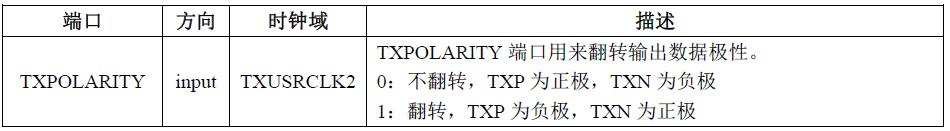

3.TX管脚极性控制

图1中③为TX 极性控制在GTX/GTH收发器结构中的位置。如果GTX/GTH收发器TXP和TXN差分管脚在PCB布线时进行了交换,差分对发送输出的比特流会取反。一种解决办法是在并串转换之前对发送的数据位逐位取反。另外一种方法是通过TX极性控制,实现TXP和TXN极性交换。图6给出了TX极性控制端口操作。

图6、TX极性控制端口操作

图7、TX管脚极性控制配置界面