作者:饿狼传说,来源:FPGA的现今未微信公众号

串并、并串转化也是FPGA设计中常见的基本问题,相对来说比较简单。如下图所示,串并转换,就是将串行输入的数据,等一定的时钟周期,“攒”到一定的数据量后,统一输出的过程。并串刚好相反。

网上有大量的说明和原理介绍了,这里不再赘述。本文仅从工程的角度,说明他们的一些应用场景。

1、接口适配

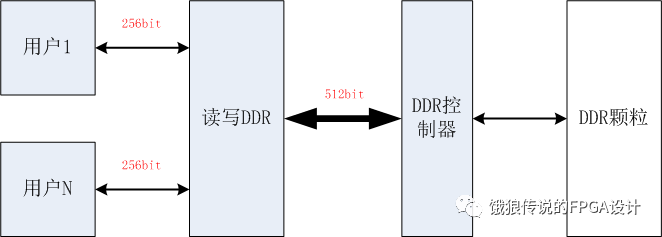

顾名思义,不同接口间数据位宽不匹配的时候,需要通过串并或者并串转换来实现位宽的一致,如下图所示:

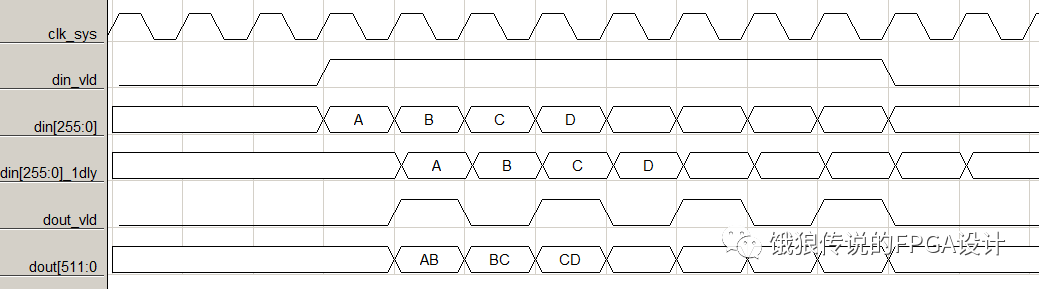

DDR控制器用户侧接口是512bit的位宽,但是左边用户内部处理的数据位宽是256bit,这个时候读写DDR就需要做一个位宽转换。在写入的时候需要将2个256bit的数据拼接成一个512bit的数据写入DDR中,在读数据的时候,需要将一个512bit的数据分成2个256bit的数据给用户。串并转换的时序图如下图所示,连续输入的数据,在输出的时候,每隔一个时钟周期,输出一个512bit数据。

并串转化的设计类似,不同的是,由于并行信号某一时刻的带宽比串行接口的带宽大,需要先将并行信号用fifo缓存,简化我们的设计。读fifo的时候遵从读一拍,停一拍,从fifo中读出的512bit的数据,分2次发送出去。

2、串口

在一些简单串口的设计中,比如UART接口,也是一种典型的串并转化,但是仔细思考就会发现,其本质也是一种接口的适配,即一端是1bit的接口,另一端是8bit的接口。其本质和第1点中例子是一样的,这里不再赘述。

在实际的串并并串转化设计中,有什么需要注意的了?要考虑信号的不连续,以上述第1个场景中描述的为例,其256bit的数据,有可能是不连续的,那么在串并转换的时候,并行信号输出的时间点就所有不同,弄清楚这点就可以了。