本文是该系列的第7篇。第2篇中以数字滤波器的设计为主题,介绍了System Generator的完整设计流程。不过仍然有些问题需要解决:

1. 如何选择一个最合适的数据类型(以最少资源达到性能需求)?

2. 如何选择系统的输出位宽(保证信号不失真)?

传统的HDL模型设计方法中,博主通常会用MATLAB进行仿真,确认位宽对数据量化的影响;或在Vivado中仿真,截取合适的滤波器输出位数。System Generator提供的相关特性可以大大简化该流程,本文将对此做介绍。

本设计使用到的block

1.Xilinx block:

2.其它block:

Digital Filter Design(DSP System Toolbox->Filtering->Filter Implementations):设计数字滤波器

这里给出了设计中用到的所有block在库中的路径,后文不再提及(前文用过的block没有给出;同一block会包含在多个库中,为了寻找方便这里只列出一个路径)。

FPGA设计与理想情况对比

虽然在第2篇的设计中观察到输出信号的频谱图确实符合设计要求,但由于经过数据转换,数据类型、位宽等问题都会影响到计算精度,我们很难评估该结果与理想情况的偏差。

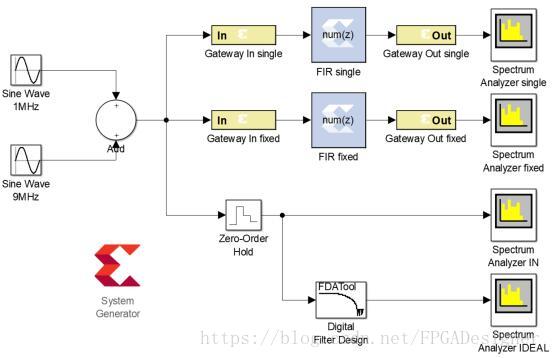

Simulink环境可近似为理想环境,因此我们将System Generator滤波结果与Simulink的滤波结果作对比。添加Digital Filter Design到model中,该block的配置界面与FDATool工具完全相同,对输入信号进行滤波。此时model如下:

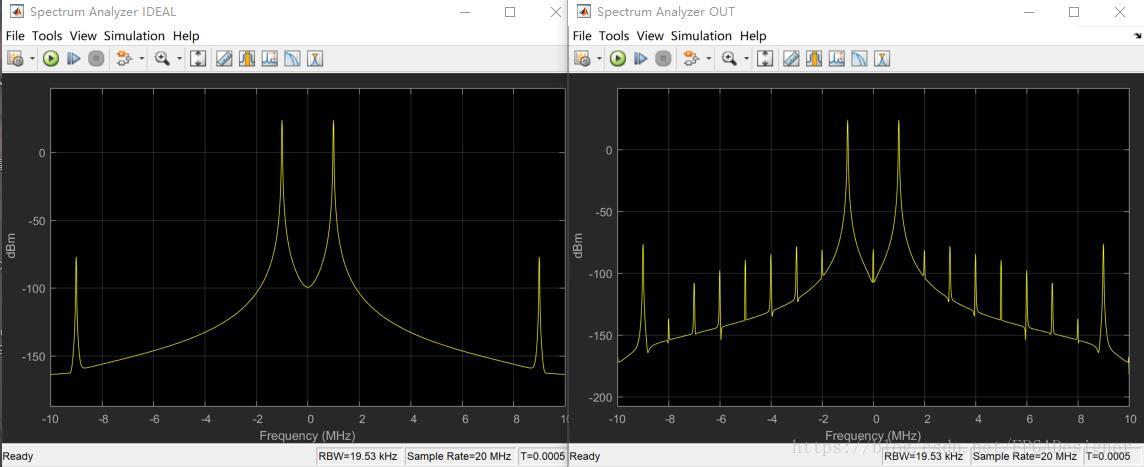

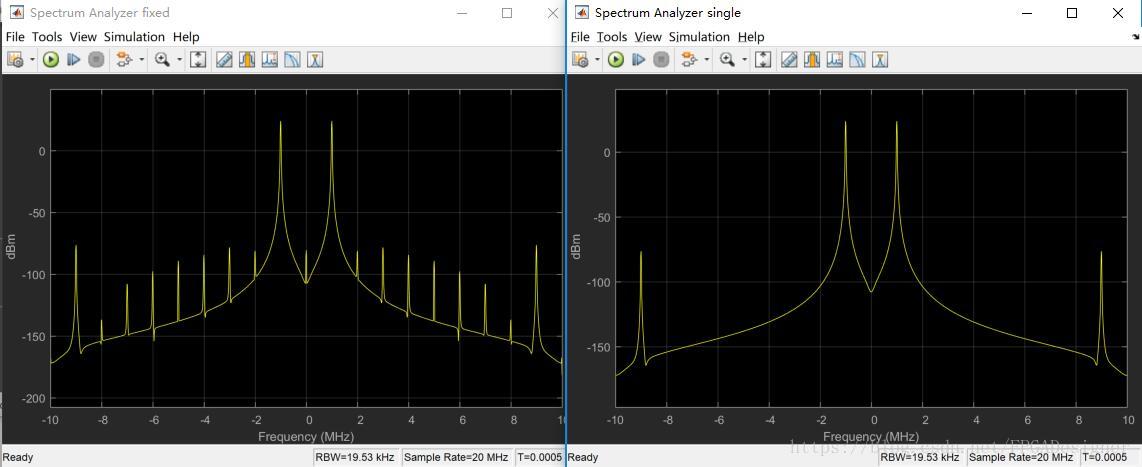

将Digital Filter Design与Digital FIR Filter的滤波器参数设置为完全相同(20Mhz采样、1.5MHz通带截止、8.5MHz阻带截止、0.01dB通带衰减、100dB阻带衰减)。运行,理想情况(左)与System Generator的输出频谱对比如下:

可以看到System Generator设计的滤波器,由于数据格式、位宽的影响,与理想情况下的频谱结果并不完全相同。对于设计者而言,需要考虑的就是这种差异是否可以接受,即是否会影响到实际的系统性能。

不同字长定点数据的对比

如果System Generator和理想情况之间的差异不能接受,就该考虑修改设计。FPGA设计可以考虑使用定点数据类型(Fixed-point)或浮点数据类型(Floating-point),但后者消耗的资源几乎是前者的十几倍甚至更多,设计中通常都采用定点数据格式。

在System Generator再添加一组滤波器设计(可以复制粘贴),将Gateway In的数据格式设置为32-30Bits定点(32表示整体位宽,30表示小数部分位宽),与原来的16-14Bits定点数据格式作对比。此时的model如下:

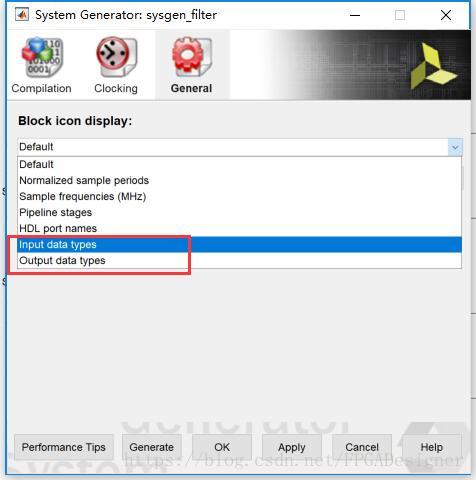

如果运行后想观察整个model中的数据类型变化,可以在System Generator的General->Block icon display中选择“Input data types”或“Output data types”。运行完成后相关信息会显示在block上。

Fixed_32_30(右)与Fixed_16_14(左)的输出频谱对比如下:

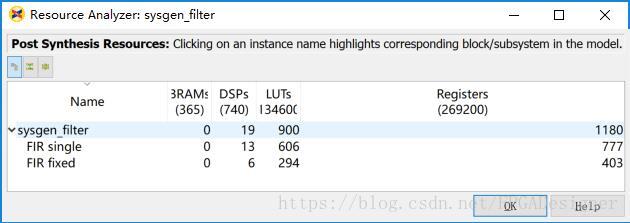

可以看到提高了定点数的位宽后,计算精度明显提高,输出信号频谱与理想情况的频谱已经几乎相同。导出设计到FPGA,运行资源分析:

可以看到增加了数据位宽后,系统使用的FPGA资源几乎增加了一倍(FIR single与FIR fixed相比)。设计者需要在资源和性能之间衡量,选择最合理的设计。用类似的方法也可以比较不同滤波器系数位宽对FIR滤波系统的影响。

系统输出位宽选择

当使用Fixed_16_14格式时,FIR滤波器的输出位宽系统会自动设定为Fixed_36_33,这是全精度输出结果。而在FPGA设计中我们经常需要截位,否则位宽在整个系统中不断积累,大大增加资源的消耗。如何确定截取的位数呢?

System Generator中有两个与此相关的block:Convert和Reinterpret,都可以进行数据的转换。Convert可以实现不同数据类型、不同位宽之间的转换,且可以设置量化和溢出的处理方式;Reinterpret可以实现数据类型之间的转换,还可以重新定义输出数据小数点的位置。

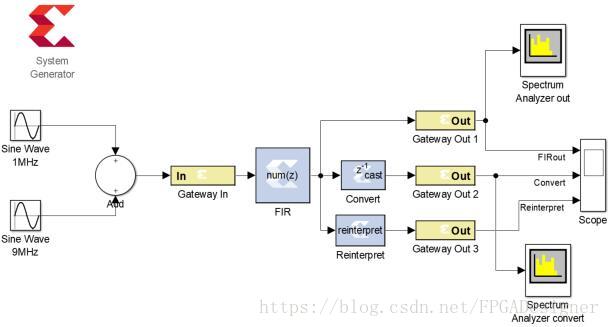

添加这两个block到model中,按下图连接:

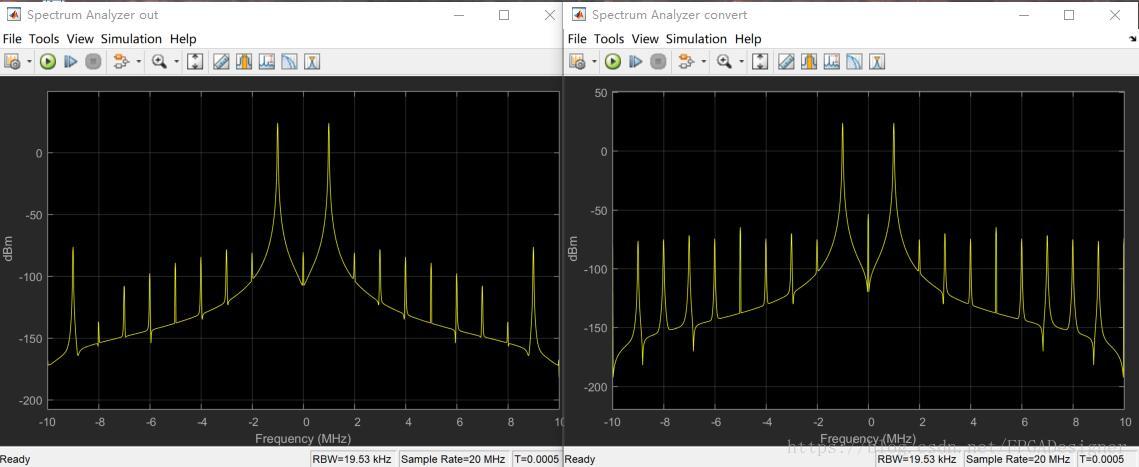

使用Convert将FIR输出的Fixed_36_33数据转换为Fixed_16_13数据;使用Reinterpret将小数点重定位在第31bit(即数据放大4倍),具体配置可参考本系列第8篇。运行仿真:

从频谱图对比可以看出,经过Convert转换后,输出信号的频谱情况进一步恶化,设计者需要考虑截位是否会影响到系统性能。

使用Scope分别观察FIR输出、Convert转换后、Reinterpret转换后的信号:

可以看到Fixed_36_33和Fixed_16_13两种数据格式的信号波形几乎完全相同(第一和第二个波形)。Reinterpret由于将小数点从33bit重新定义到了31bit,相当于放大了4倍,输出信号的范围扩展为-4~4(Sine Wave block输出信号的幅度设置为1)。

将用作测试端口的Gateway设置为不作为output,导出到FPGA中后,滤波器输出位宽只有16Bits(第2篇没有截位的设计为输出36Bits)。

Scope使用技巧

在第2篇中已经介绍了如何用Scope观察多路信号,本文不再赘述。这里在介绍两个设计技巧:

1.设置显示范围。

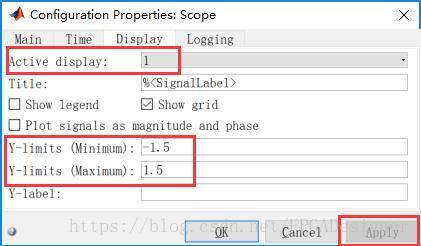

在View->Configuration Properites:Scope->Display中可以设置波形显示范围。Active display选择信号通道,设置Minimum和Maximum。点击Apply即可应用该设置。

2.设置信号名称。

在Simulink模型中,双击接入Scope的连线,即可出现一个编辑框(同时线变为蓝色),输入的名称将作为Scope中波形窗口的title(也可以在上图中的“Title”编辑框中设置)。

文章来源:FPGADesigner的博客

*本文由作者授权转发,如需转载请联系作者本人